# EPOS for Raspberry Pi

Software/Hardware Integration Lab at UFSC

# EPOS for Raspberry Pi

## Table of contents

- EPOS for Raspberry Pi

- 1. Running EPOS on Raspberry Pi

- 1.1. Compiling

- 1.2. Running and Debugging

- 1.3. Running Raspberry Pi3b in a real Hardware

- 1.3.1. Setting up the SD Card

- 1.3.1.1. Firmware Files

- 1.3.1.2. Application Image

- 1.3.2. Connecting the UART to your PC

- 2. ARMv8 and AArch64

- 3. System Calls in ARMv8 with AArch64

- 3.1. Introdução

- 3.2. Motivação

- 3.3. Exception Levels no ARMv8

- 3.3.1. Registradores Especiais do AArch64

- 3.4. A Instrução SVC

- 3.5. Exemplo de uma System Call no Linux (em ARMv8)

- 3.6. Implementação de uma System Call no ARMv8: Exception Handling

- 3.7. Demonstração Bare Metal

- 3.8. System Call Reentrante

- 3.9. Referências

- 4. ARMv7 and AArch32

- 5. Cortex-A53

- 6. Task Memory Model

- 6.1. O modelo de memória de um processo

- 6.1.1. Espaços de endereçamento

- 6.2. System calls

- 6.2.1. Execução

- 6.2.2. Exemplo

- 6.3. Switch context

- 6.3.1. Principais causas para a troca de contexto entre processos

- 6.4. Kernel space

- 6.5. Referências

- 7. MMU for Paging

- 7.1. Conceitos importantes

- 7.2. MMU

- 7.3. Paging

- 7.4. MMU - ARMv7

- 7.5. Paging - ARMv7

- 7.5.1. Super Section

- 7.5.2. Section

- 7.5.3. Large Page

- 7.5.4. Small Page

- 7.6. Exemplo de tradução de endereço no ARMv7

- 7.7. Ativação da MMU no ARMv7

- 7.8. Referências

- 8. Task Context Switching

- 8.1. What is Context Switching

- 8.2. How does a Context Switching happen

- 8.3. What is a PCB

- 8.4. Performance considerations

- 8.4.1. Translation Lookaside Buffer

- 8.4.2. Address Space Identifier

- 8.4.2.1. ASID on Context Switch

- 8.4.2.2. Limitation of ASID

- 8.5. Switching Context in ARMv7/Raspberry Pi3

- 8.5.1. ARM Processor Mode

- 8.5.2. IRQ

- 8.5.3. Managing Address Spaces

- 8.5.3.1. Accessing translation table support registers

- 8.6. Validation code

- 8.7. References

- 9. System Calls

- 9.1. Motivação

- 9.2. Definição de System Call

- 9.3. Métodos de Implementação

- 9.4. Funcionamento no ARMv7 e Cortex-A53

- 9.4.1. System Calls na arquitetura ARMv7

- 9.4.2. System Calls na família Cortex-A

- 9.5. Como iniciar uma system call

- 9.5.1. Registradores

- 9.5.2. Instruções

- 9.5.2.1. SVC - Supervisor Call

- 9.5.2.2. HVC - Hypervisor Call

- 9.5.2.3. SMC - Secure Monitor Call

- 9.5.2.4. SRS - Store Return State

- 9.5.3. Parâmetros

- 9.6. Identificação do tipo de exceção

- 9.6.1. System calls aninhadas

- 9.7. Identificação da system call

- 9.8. Como retornar de uma system call

- 9.8.1. Instruções

- 9.8.1.1. RFE - Return From Exception

- 9.8.1.2. ERET - Exception Return

- 9.8.2. Valor de retorno

- 9.9. Referências

- 10. System Object Proxies and Agents

- 10.1. Gerenciamento de Syscalls

- 10.1.1. Stubs

- 10.1.2. Agents

- 10.2. Sugestão de Implementação

- 10.2.1. Implementação da Mensagem

- 10.2.2. Implementação de Stubs

- 10.2.3. Implementação dos Agentes

- 10.3. Referências

- 10.4. Autores

- 11. Resource Management

- 11.1. Resource Management in Multitasking

- 11.1.1. Memory

- 11.1.2. Processing Time

- 11.2. Desalocação de recursos

- 11.3. EPOS Multitasking

- 11.4. Exemplo de Implementação

- 11.4.1. Classe Task

- 11.4.2. Ponteiro para Task nos Elementos

- 11.4.3. Adição dos Elementos nas listas da Task

- 11.4.4. Criação da Task

- 11.4.5. Destructor da Task

- 11.5. Resource Management Autores

- 11.6. Resource Management Referências

- 12. Inter-Process Communication

- 12.1. Motivação

- 12.2. Modelos de IPC

- 12.2.1. Memória Compartilhada

- 12.2.2. Troca de Mensagens

- 12.2.2.1. Comunicação Direta

- 12.2.2.2. Comunicação Indireta

- 12.2.2.3. Comunicação Síncrona ou Assíncrona

- 12.2.2.4. Buffers

- 12.2.2.5. Pipes

- 12.2.2.5.1. Unnamed pipes

- 12.2.2.5.2. Named pipes

- 12.2.2.6. Sockets

- 12.3. Exemplo de implementação

- 12.3.1. Memória compartilhada

- 12.3.2. Troca de mensagens

- 12.3.2.1. Troca de mensagem assíncrono

- 12.3.2.2. Troca de mensagem síncrona

- 12.4. Referências

- 13. I/O

- 13.1. Memory Mapped Peripherals

- 13.2. Registradores de dispositivo

- 13.3. Direct Memory Access(DMA)

- 13.4. Memory Mapped Regions

- 13.5. Níveis de Privilégio

- 13.6. Controle de nível de privilégio

- 13.7. Bits para controle de privilégio de uma região

- 13.7.1. Modelo de permissões de acesso AP 2: 1

- 13.7.2. Modelo de permissões de acesso AP 2: 0

- 13.8. Single-channel DMA transfer

- 13.9. Dual-channel DMA transfer

- 13.10. Referências

## 1. Running EPOS on Raspberry Pi

### 1.1. Compiling

To compile an APP for Raspberry Pi3b, first configure the application *Traits<Build>* as follows:

```

template<> struct Traits<Build>: public Traits<void> { static const unsigned int MODE = LIBRARY; static const unsigned int ARCHITECTURE = ARMv7; // You can use ARMv8 or ARMv7 on QEMU. static const unsigned int MACHINE = Cortex; static const unsigned int MODEL = Raspberry_Pi3; static const unsigned int CPUS = 1; // or 4 static const unsigned int NODES = 1; // (> 1 => NETWORKING) static const unsigned int EXPECTED_SIMULATION_TIME = 60; // s (0 => not simulated, using real hardware) };

```

At the directory where you installed EPOS' source code, just type:

```

$ make APPLICATION=<appname>

```

## 1.2. Running and Debugging

To run and debug applications, follow the steps described in [EPOS documentation](#).

## 1.3. Running Raspberry Pi3b in a real Hardware

First, to run an application in real Raspberry Pi3 hardware, use ARMv8 as the ARCHITECTURE in Traits<Build>. In EPOS, ARMv8 is very similar to ARMv7, it just replaces the cores() function in cpu.h, as Raspberry Pi3b hardware does not support the ARMv7 implementation of cores() function.

### 1.3.1. Setting up the SD Card

To boot a Raspberry Pi3b in a real hardware, you first need to configure an SD Card with the EPOS application image and some additional firmware files required by the Raspberry Pi3b hardware.

#### 1.3.1.1. Firmware Files

The additional Firmware files required are available at the [Raspberry Pi3b Official Github](#). From the firmware folder, you only need bootcode.bin and start.elf files. Setup the SD card with a single partition, fat32, and copy the bootcode.bin and start.elf files to the SD card.

#### 1.3.1.2. Application Image

Raspberry Pi3b CPU boot is started by the GPU. The GPU reads the SD card and copies the kernel image to the specific initial address, where the first piece of code in this image is expected to be the Vector Table. The default image names are related to the compatibility to Pi models. You can specifically select your own name in config.txt. Considering no config.txt override, the search order for a Pi3 is:

```

if kernel8.img is found: boot in 64 bits mode else if any of kernel8-32.img, kernel7.img, or kernel.img are found: boot in 32 bits mode

```

The address of the Vector Table changes from 64 and 32 bits modes. For 32 bits, the vector table is initially located at the address 0x00008000, and 0x00080000 for 64 bits.

Currently, EPOS supports only 32 bits Raspberry Pi3b. Thus, after compiling, copy the final application binary file to the SD card, renaming it to kernel8-32.img or kernel7.img or kernel.img.

### 1.3.2. Connecting the UART to your PC

**Warning:** Attain to the Raspberry Pi3b energy supply requirements, and to the correct pin connection when connecting the RaspberryPi3b UART / FTDI / PC.

EPOS uses Raspberry MiniUART as the default Serial Display. To connect the RaspberryPi 3b UART to your PC, an FTDI is needed to intermediate the UART pins and connect the EPOS app output to the PC USB over serial protocol. The following configuration is then needed:

|      |             |

|------|-------------|

| FTDI | Pi3b        |

| TX   | RX (pin 10) |

| RX   | TX (pin 8)  |

| GND  | GNC (pin 6) |

After connecting the FTDI to PC using a USB cable, the Raspberry Pi3b output can be seen by reading the USB content (e.g., using minicom or cutecom). The UART configuration is the following:

|              |        |

|--------------|--------|

| Baudrate     | 115200 |

| Data bits    | 8      |

| Stop bits    | 1      |

| Parity       | None   |

| Flow Control | None   |

## 2. ARMv8 and AArch64

## 3. System Calls in ARMv8 with AArch64

### 3.1. Introdução

O conjunto de chamadas de sistema (syscalls) é a interface entre o sistema operacional e seus programas aplicativos, sendo esta utilizada para que a aplicação a nível de usuário requisite serviços privilegiados a nível do kernel do sistema operacional. Estes serviços podem ser relacionados à hardware, tal como acessar um disco rígido, ou relacionado ao sistema operacional, como a criação de novos processos.

Esta interface, separa o ambiente em que o usuário tem controle, daquele que ele não tem, que seria o kernel. Portanto uma system call irá executar de forma bastante restritiva e sem controle do programa de usuário, visto que irá operar sobre estruturas críticas do sistema operacional.

Se o programa de usuário tivesse acesso a funções do kernel sem esta interface, há a possibilidade deste programa corromper outras aplicações, acessar memória que não tem autorização e até mesmo corromper o sistema operacional como um todo.

De forma geral, alguns tipos de chamadas de sistema são:

- Gerenciamento de processo

- fork

- waitpid

- Gerenciamento de arquivos

- open

- close

- read

- write

- Gerenciamento do sistema de diretório e arquivo

- mkdir

- rmdir

- mount

- Diversas

- chmod

- kill

- time

Uma forma de implementar uma syscall é forçar uma exceção de hardware que por sua vez irá chamar o tratador de interrupções/exceções. Algumas arquiteturas possuem instruções específicas para system calls, o que é o caso do ARMv8 que possui uma instrução chamada Supervisor Call (SVC) que irá executar o serviço do sistema operacional que foi requisitado.

### 3.2. Motivação

Um uso comum de chamadas de sistema para SOs como o Linux é criar uma separação entre espaço de usuário e de sistema. Assim, os serviços do sistema são acessados apenas via system calls o que implica em:

- maior segurança do sistema operacional sob as aplicações, visto que essas não terão acesso direto às estruturas e funções internas do sistema; e

- nível maior de compatibilidade binária entre arquivos compilados por diferentes versões do Linux, pois uma chamada de sistema permanece a mesma: uma única execução da instrução de system call em vez de uma chamada de função direto para o endereço na biblioteca do kernel.

### 3.3. Exception Levels no ARMv8

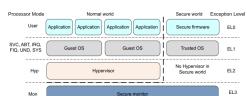

No ARMv8, a execução acontece em um de 4 Exception Levels. No AArch64 cada exception level está associado com um nível de privilégio, de forma similar aos PL (Privilege Levels) do ARMv7.

- **EL0** possui o menor nível de privilégio e será onde as aplicações de usuário executarão;

- **EL1** agrupa, tipicamente, o Kernel do sistema operacional, e portanto neste nível que serão executadas as system calls do SO. Visto que o espaço de usuário é em EL0 e as system calls estão em EL1, a aplicação precisa executar a instrução SVC (Supervisor Call) para provocar uma exceção síncrona e elevar o seu Exception Level para EL1.

- **EL2** é o nível de exceção onde o Hypervisor executará. Para elevarmos para este nível, a partir do EL1, devemos utilizar a instrução HVC

- **EL3** o nível de exceção de maior privilégio, e será onde teremos o firmware de baixo nível executando, que tipicamente seria o Secure Monitor. Para subir à este nível utiliza-se a instrução SMC.

Em cada Exception Level, o processador tem um modo de execução diferente, como pode ser visto na tabela abaixo. No caso quando executamos a instrução SVC, além de subirmos para o EL1, estamos mudando o modo do processador para SVC.

**Figura:** Exception Levels e Processor Modes do ARMv8

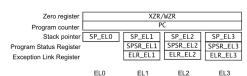

### 3.3.1. Registradores Especiais do AArch64

Além do mais, em cada EL, teremos um conjunto de registradores especiais. Dois deles servirão para o salvamento de contexto ao tratar uma exceção:

- **SPSR\_ELn** (Saved Program Status Register): salva o estado do processo PSTATE quando uma exceção é tomada. Teremos um SPSR para cada Exception Level (com exceção do 0), portanto o n será substituído por 1, 2 ou 3

- **ELR\_ELn** (Exception Link Register): armazena o endereço de retorno do nível em que ocorreu a exceção. Novamente teremos um desse registrador para EL com exceção do 0. Portanto o ELR\_EL1 irá armazenar o endereço de retorno de uma exceção que ocorreu no EL0 e assim por diante

Teremos também um SP (Stack Pointer) para cada Exception Level. O PC (Program Counter) e o XZR/WZR (registrador zero) é o mesmo em todos os Exception Levels.

## 3.4. A Instrução SVC

Para uma aplicação de usuário chamar uma syscall ela deve definir os 32 bits inferiores do registrador x8 com o número da syscall que deseja-se chamar, deve também, se necessário, passar os argumentos nos registradores x0 à x4, e por fim emitir a instrução svc 0. O valor de retorno da system call estará disponível no registrador x0 após a instrução SVC.

Ao executar esta instrução, a execução da aplicação será interrompida pela execução da system call por parte do Kernel

A sintaxe da instrução svc é a seguinte:

svc {cond} #imm

- **imm:** expressão que é avaliada para um número inteiro. Ela é ignorada pelo processador, mas pode ser usada pelo tratador de interrupções para saber qual é o serviço requisitado.

- **cond:** condição opcional que as instruções da arquitetura ARMv8 possuem que verifica flags setadas por instruções anteriores para decidir se o svc será ou não executado.

## 3.5. Exemplo de uma System Call no Linux (em ARMv8)

O programa abaixo faz uma simples operação de escrever "Hello World!" no stdout e faz a system

call exit:

```

.global _start .section .text _start: // write system call mov x8, #64 // Passing the syscall number

in decimal mov x0, #1 // File descriptor. 1 is stdout ldr x1, =message // Loading to x1 mov x2,

#12 // Length of what we are writing svc 0 // Invoke syscall // exit system call mov x8, #93 mov x0,

#41 // Passing a dummy error code svc 0 .section .data message: .ascii "Hello World\n"

```

A função `_start` é o ponto de início do programa. A chamada de sistema relacionada à escrita em arquivo é a `write` e o número dela de acordo com a tabela de system calls do ARMv8.

A tabela com a especificação dos códigos de syscall do Linux para ARM64 (que implementa ARMv8) pode ser encontrada no seguinte link:

[https://chromium.googlesource.com/chromiumos/docs/+/master/constants/syscalls.md#arm64-64\\_bit](https://chromium.googlesource.com/chromiumos/docs/+/master/constants/syscalls.md#arm64-64_bit)

A primeira instrução é responsável por escrever o número da system call no registrador X8.

Revisando a tabela de syscalls, o primeiro argumento é o número correspondente ao descritor de arquivo no qual a escrita será feita, que no caso do valor 1 trata-se do descritor de arquivo referente ao `stdout`, então o registrador X0, que guarda o primeiro argumento, é carregado com o valor 1.

O segundo argumento é o início do buffer que guarda o conteúdo a ser escrito, então no registrador X1 é guardado o endereço do dado estático que representa a string “Hello World!\n”. Esse endereço é referenciado pela label `message`.

O terceiro e último argumento é quantos bytes desse buffer serão copiados para a saída definida no primeiro argumento. A string “Hello World!” codificada em ASCII ocupa exatos 12 bytes, com a quebra de linha representada pelo \n o tamanho total fica 13 bytes.

Por último, a instrução `svc` é chamada com o valor 0. Esse valor é escolhido pois o imediato precisa de algum valor que não será necessariamente usado, e o valor da system call já está em X8.

Após a system call de `write`, é feita a system call do `exit`, que possui número 93 e recebe um argumento no registrador x0, que é o código de erro que será retornado. Após a compilação e execução deste código, em SOs Linux pode-se verificar o valor de retorno de uma aplicação com ‘`echo $?`’, que no caso desta aplicação irá retornar 41.

A tabela com a especificação dos códigos de syscall para ARM64 (que implementa ARMv8) pode ser encontrada no seguinte link:

[https://chromium.googlesource.com/chromiumos/docs/+/master/constants/syscalls.md#arm64-64\\_bit](https://chromium.googlesource.com/chromiumos/docs/+/master/constants/syscalls.md#arm64-64_bit)

### 3.6. Implementação de uma System Call no ARMv8: Exception Handling

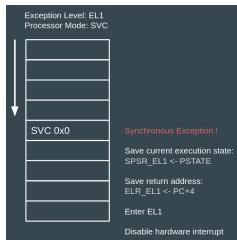

Quando uma exceção ocorre, o processador necessita trocar para o Exception Level que dê suporte para o tratamento da exceção, ou seja, nenhuma exceção será tratada em EL0, que é o nível da aplicação.

Portanto uma exceção causará uma alteração no fluxo do programa, seguido de uma alteração de

Exception Level e Processor Mode, tornando necessário o salvamento do contexto para que possamos voltar depois a executar a aplicação.

Visto que a instrução SVC provoca uma elevação de nível de privilégio para o EL1, será feito o uso dos registradores SPSR\_EL1 e ELR\_EL1 para salvamento do contexto do programa aplicativo.

**Figura:** Execução de um programa aplicativo interrompida por uma exceção síncrona

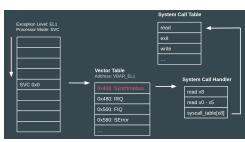

Feito isto, o PC será setado para o vetor da Vector Table que possui o Tratador de Exceção correspondente a exceção que estamos tratando. Para descobrir o endereço deste vetor, tomaremos como base o endereço base da Vector Table, disponível no registrador VBAR\_EL1, e somaremos a este endereço o offset do tratador da exceção corrente.

Portanto a Vector Table, de modo geral, é uma tabela de Tratadores de Exceção, sendo que esta tabela contém instruções a serem executadas, ao invés de um conjunto de endereços. Cada vetor da tabela possui tamanho de 32 instruções, e como cada instrução no ARMv8 possui 4 bytes, teremos que os vetores serão espaçados entre si por 128 bytes (ou 0x80 bytes)

Note também que teremos uma Vector Table para cada Exception Level a partir do 1, portanto teremos também VBAR\_EL2 e VBAR\_EL3.

| Address                | Exception type         | Description         |

|------------------------|------------------------|---------------------|

| VBAR_EL1 + 0x000       | Synchronous            | Current EL with SP0 |

| + 0x000 IRQ+IRQ        |                        |                     |

| + 0x100 FIQ+FIQ        |                        |                     |

| + 0x180 SError+vSError |                        |                     |

| + 0x200 Synchronous    | Current EL with SPx    |                     |

| + 0x200 IRQ+IRQ        |                        |                     |

| + 0x300 FIQ+FIQ        |                        |                     |

| + 0x380 SError+vSError |                        |                     |

| + 0x400 Synchronous    | Lower EL using AArch64 |                     |

| + 0x400 IRQ+IRQ        |                        |                     |

| + 0x500 FIQ+FIQ        |                        |                     |

| + 0x580 SError+vSError |                        |                     |

| Address                | Exception type         | Description |

|------------------------|------------------------|-------------|

| + 0x000 Synchronous    | Lower EL using AArch32 |             |

| + 0x000 IRQ+IRQ        |                        |             |

| + 0x100 FIQ+FIQ        |                        |             |

| + 0x200 SError+vSError |                        |             |

**Figura:** Offsets da Vector Table relativo ao endereço da Vector Table

A exceção provocada por SVC é uma exceção síncrona, uma vez que esta foi provocada pela execução de uma instrução, e portanto será tratada pelo Exception Handler em 0x400, pois viemos de um EL abaixo (do EL0 ao EL1) e estamos usando o modo AArch64.

Uma exceção síncrona pode ter diversos motivos, e para que seja possível distinguir cada motivo, no tratador de exceção será consultado o Exception Syndrome Register, que irá conter informações necessárias para determinar a razão da exceção:

- Bits **31:26**: classe da exceção, que pode ser unallocated instruction, data abort, SVC, HVC, entre outros.

- Bit **25**: indicará o tamanho da instrução que provocou a exceção: 0 se for de 16 bits e 1 se for de 32 bits

- Bits **24:0**: contém informação específica para cada classe de exceção. No caso de uma exceção

SVC, este campo contém o valor imediato da instrução SVC, que de acordo com os nossos exemplos será 0.

Após identificar que trata-se de uma exceção do tipo SVC 0 (system call), é chamado o system call handler, que irá indexar a tabela de system calls com o número da system call que foi requisitada e ler e encaminhar os argumentos que foram passados pela aplicação para a system call correspondente.

A system call por sua vez irá executar um conjunto de instruções que exigem um nível de privilégio superior ao de uma aplicação e que podem vir a envolver o kernel do sistema operacional, de forma a satisfazer o serviço que foi requisitado pela aplicação. Por fim, a system call retorna para o system call handler, este por sua vez retorna para o exception handler, e este irá retornar para o fluxo da aplicação por meio da instrução ERET (Exception Return).

A instrução ERET finaliza o tratamento da exceção e retorna ao Exception Level anterior à exceção, que no caso de uma system call será o EL0. Para que seja possível retornar ao contexto da aplicação, esta instrução irá fazer com que o SPSR\_EL1 seja copiado para o PSTATE, e que o ELR\_EL1 seja copiado para o PC.

Voltando ao contexto da aplicação, volta-se a seguir o fluxo da aplicação.

### 3.7. Demonstração Bare Metal

Arquivos de destaque:

- **exc.c:** Exception Handler, Syscall Handler e Syscall Table

- **main.c:** Inicializa o UART, MMU e provoca uma exceção síncrona

- **start.S:** Código assembly para setup e Vector Table

O código fonte encontra-se disponível em: <https://github.com/JPADN/syscall-bare-metal>

Leia o README.md para instruções de compilação e execução.

Tudo começa em main.c, onde temos um bloco asm que irá demonstrar uma aplicação chamando uma system call. Primeiramente, o programa de usuário irá salvar na pilha os registradores que vão ser utilizados pela system call por meio da instrução str. Logo após são passados os argumentos da system call nos registradores x0 à x5, e o número da system call que deseja-se executar no registrador x8. Por fim executa-se a instrução SVC.

```

void main()

{

unsigned long i=0;

// set up serial console

setSerial();

// set up ping

setPing();

// perform a system call here

// to do something like:

/*for(i=0;i<10;i++)

{

if((i%2)==0)

cout<<"#<#";

else

cout<<"#*<#";

}

cout<<endl;

*/

// now do some work

for(i=0;i<10;i++)

{

cout<<"#<#";

cout<<"#*<#";

}

cout<<endl;

}

```

Como foi visto anteriormente, a instrução SVC irá provocar uma exceção síncrona, e portanto o fluxo de execução mudará para o vetor da vector table que irá tratar essa exceção. A vector table está definida em start.S.

start.S trata-se de um arquivo em linguagem assembly que tem a função de fazer o setup inicial do Raspberry Pi que estamos emulando, que envolve instruções para forçar o uso de apenas uma CPU, verificar em qual EL a máquina foi bootada, e principalmente (para o contexto deste seminário), configurar o registrador VBAR EL1 para apontar para a nossa Vector Table.

```

// set up exception handlers

ldr    x2, =_vectors

msr    vbar_el1, x2

```

```

vectors:

// synchronous

.align 7

.nov  x6, #0 // Passing exception type

.ln    exc_handler

.erre

// IRQ

.align 7

.nov  x6, #1

.bl    exc_handler

.erre

// FIO

.align 7

.nov  x6, #2

.bl    exc_handler

.erre

// SError

.align 7

.nov  x6, #3

.bl    exc_handler

.erre

```

Cada vetor da Vector Table irá setar o registrador x6 para um número que identifique o tipo de exceção, e fazer um branch and link para o Exception Handler (função em C), que será o mesmo para todas as exceções. Ao término do tratamento da exceção, executamos eret para voltar ao contexto anterior a exceção.

Visto que vamos tratar uma exceção síncrona, iremos setar x6 para 0 e fazer um branch para o exception handler.

O exception handler está definido em exc.c. Ao entrarmos nele, iremos ler os registradores da system call (de x0 à x5 estarão os argumentos e em x8 o número da system call), o registrador x6 para poder identificar o tipo de exceção, e também iremos ler os registradores de sistema do ARM, que são: ESR EL1, ELR EL1, SPSR EL1, FAR EL1 e CurrentEl.

```

// main() - our main application code

// Since we are working with 64 bit registers, we use long 64 variables (second arg is 8 bytes)

long long reg[8]; // 64 bit register, reg, current_val // System Registers for G12

// Reading system call registers

void read_syscall_registers()

{

// Reading System Call arguments (reg[0] to reg[3])

reg[0] = Mdr(); // Mdr() // Reading System Call arguments (reg[0] to reg[3])

reg[1] = Dr0();

reg[2] = Dr1();

reg[3] = Dr2();

reg[4] = Dr3();

reg[5] = Dr4();

reg[6] = Dr5();

reg[7] = Dr6();

// Reading System Call return values (reg[8] to reg[11])

reg[8] = Dr7();

reg[9] = Dr8();

reg[10] = Dr9();

reg[11] = Dr10();

}

// Reading CPU Registers and Current

void read_registers()

{

// Reading CPU Registers

reg[0] = Rr0(); // Rr0() // Reading CPU Registers

reg[1] = Rr1();

reg[2] = Rr2();

reg[3] = Rr3();

reg[4] = Rr4();

reg[5] = Rr5();

reg[6] = Rr6();

reg[7] = Rr7();

// Reading Current

reg[8] = Cr0(); // Cr0() // Reading Current

reg[9] = Cr1();

reg[10] = Cr2();

reg[11] = Cr3();

}

// Writing CPU Registers

void write_registers()

{

// Writing CPU Registers

Cr0();

Cr1();

Cr2();

Cr3();

}

```

Feito isto, iremos printar no terminal qual o tipo de exceção que estamos tratando, a partir da leitura do registrador x6.

Logo após, iremos utilizar o ESR\_EL1 (Exception Syndrome Register) com um bit shift para a direita de 26 casas, a fim de termos o campo Exception Class (Bits 31:26) do registrador ESR\_EL1 e distinguir qual a causa da exceção, que no nosso caso será uma system call.

Será chamado então o System Call Handler (`syscall_handler()`), que irá receber os argumentos e o número da system call, irá indexar a System Call Table (`syscall_table[]`) com o número da system call requisitada. Serão repassados os argumentos para a system call requisitada e esta por sua vez irá iniciar sua execução.

```

#define SYSCALL_TABLE_LEN 4

const unsigned long (*syscall_table[SYSCALL_TABLE_LEN])() = {

syscall_a,

syscall_b,

syscall_c,

syscall_d,

};

```

Nesta demonstração, temos quatro system calls ilustrativas, isto é, elas não desempenham uma operação com o kernel do sistema operacional, pois nem temos um sistema operacional neste contexto. Portanto são funções simplórias que apenas fazem um print no terminal. A `syscall_b` é diferente das outras, e irá printar no terminal também os argumentos que foram passados a ela e retornar a soma destes argumentos.

Este valor será retornado para o exception handler que irá mover este valor para registrador x0, de modo a seguir a convenção de system calls do ARMv8.

Ao retornar do exception handler, será executada a instrução `eret` como visto anteriormente, e portanto voltaremos ao contexto da aplicação. Retornando para a aplicação, será restaurado o contexto anterior a `system call` que estava armazenado na pilha e printado no terminal o valor de retorno da `system call`.

### 3.8. System Call Reentrant

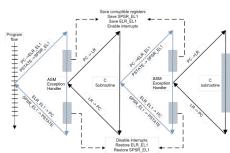

A diferença entre um tratador reentrante e um não reentrante é que durante a execução de um reentrante as interrupções que não são do mesmo tipo que está sendo tratado no momento podem ocorrer normalmente sem afetar a corretude da execução.

Um tratador de interrupções começa com as interrupções desabilitadas, e portanto se o seu tempo de execução for longo demais a ponto de que deveria ocorrer outra exceção durante o seu tratamento, ela será perdida. Este é um cenário que poderia vir a acontecer no caso de system calls, visto que pode haver uma latência na comunicação com o kernel.

Um tratador reentrante, nesse caso, salva na pilha informações essenciais para o tratamento da interrupção de forma que ele possa habilitar logo em seguida as interrupções novamente.

Abaixo temos um exemplo de um tratador de exceções que não é reentrante, esse exemplo simplesmente carrega os registradores do coprocessador com informações sobre a exceção e quatro

argumentos da exceção (x0, x1, x2, x3).

```

Exception_Handler: // Storing in the stack STP X0, X1, [SP, #-16]! STP X2, X3, [SP, #-16]! //

Reading System Registers MRS X0, ESR_EL1 MRS X1, ELR_EL1 MRS X2, SPSR_EL1 MRS X3,

FAR_EL1 ... LDP X2, X3, [SP], #16 LDP X0, X1, [SP], #16 ERET

```

Para modificar esse tratador de forma que ele se torne reentrante seria necessário permitir que interrupções aconteçam novamente, e então chamar a subrotina do tratador, que no nosso exemplo é um tratador de exceções síncronas, ou seja, exceções provocadas pela instrução SVC. Após o término do tratamento da exceção, as interrupções são desabilitadas, e os valores de SPSR\_EL1, ELR\_EL1, e de registradores “sujáveis” são restaurados da pilha.

```

Exception_Handler: // Storing in the stack STP X2, X3, [SP, #-16]! STP X0, X1, [SP, #-16]! //

Reading System Registers MRS X0, ESR_EL1 MRS X1, ELR_EL1 MRS X2, SPSR_EL1 MRS X3,

FAR_EL1 STP X0, X1, [SP, #-16]! STP X2, X3, [SP, #-16]! BL identify_and_clear_source // Read

interrupt source, clearing interrupt in controller MSR DAIFClr, #0b0010 BL C_Sync_Handler

MSR DAIFSet, #0b0010 LDP X2, X3, [SP], #16 LDP X0, X1, [SP], #16 MSR ESR_EL1, X0 MSR

ELR_EL1, X1 MSR SPSR_EL1, X2 MSR FAR_EL1, X3 LDP X2, X3, [SP], #16 LDP X0, X1, [SP],

#16 ... ERET

```

A diferença para o não reentrante é a seguinte:

1. Após mover os valores de ESR, SPSR, ELR e FAR dos registradores de coprocessador para os registradores AFIH, eles são postos na pilha.

2. Em seguida ocorre um Bl que irá para uma rotina que deve garantir que a

3. É exalida a instrução MSR DAIFClr, #0b0010 para permitir que interrupções sejam gerenciadas. Impõe o bit da máscara de interrupções.

4. O bit é definido para uma rotina em que é feita a leitura do bit de interrupção.

5. Após o tratamento as interrupções são desabilitadas setando o bit de

6. Então, o valor previo dos coprocessadores também é restaurado.

7. E por último, o valor inicial dos registradores é restaurado da pilha.

### 3.9. Referências

Sistemas Operacionais projeto e implementação, Andrew S. Tanembaum e Albert S. Woodhull. 4<sup>a</sup> edição

<https://eastrivervillage.com/Anatomy-of-Linux-system-call-in-ARM64/>

ARM Cortex-A Series Programmer's Guide for ARMv8-A

Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile

<https://github.com/bztsrc/rasp3-tutorial>

<https://developer.arm.com/documentation/100933/0100/Interrupt-handling>

## 4. ARMv7 and AArch32

## 5. Cortex-A53

## 6. Task Memory Model

### 6.1. O modelo de memória de um processo

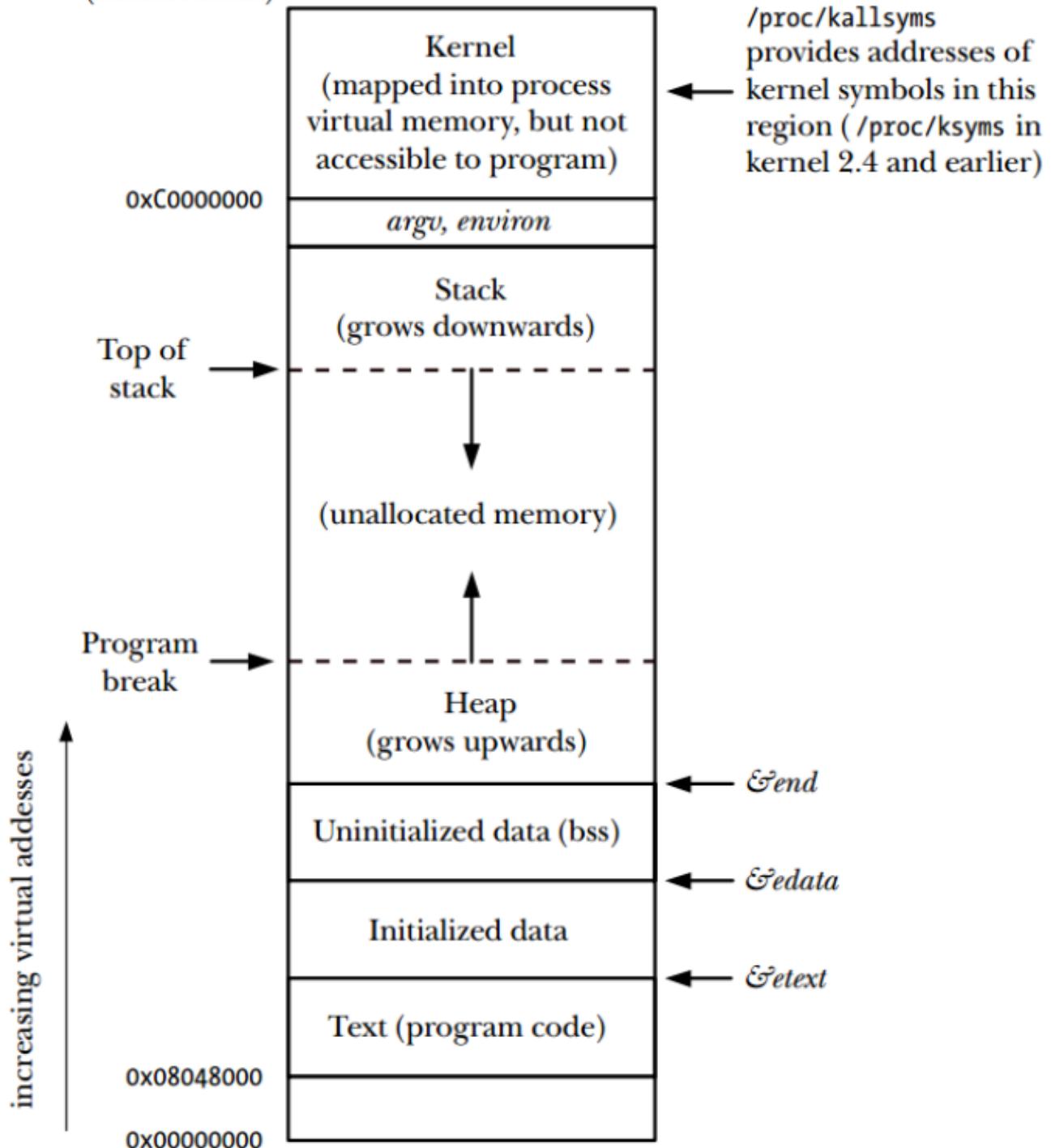

Um processo é uma instância de um programa em execução. A memória alocada para cada processo é composta por diversas partes, geralmente denominadas **segmentos**. Os principais segmentos de um processo são:

- **Segmento de texto:** o segmento de texto contém instruções de máquina do programa o qual o processo está executando. O segmento de texto é marcado com a permissão de somente leitura para que o processo não modifique accidentalmente suas próprias instruções com um valor de ponteiro incorreto. Uma vez que múltiplos processos podem estar executando o mesmo programa, o segmento de texto é marcado como compartilhado, de modo que uma única cópia do código do programa pode ser mapeada para o espaço de endereçamento de todos os processos.

- **Segmento de dados inicializados:** o segmento de dados inicializados contém variáveis globais e estáticas que foram explicitamente inicializadas. Os valores destas variáveis são lidas do arquivo executável quando o programa é carregado para a memória.

- **Segmento de dados não-inicializados:** o segmento de dados não inicializados contém variáveis globais e estáticas que não são explicitamente inicializadas. Antes de iniciar o programa, o sistema inicializa toda a memória neste segmento com o valor 0. Por razões históricas, este segmento é frequentemente chamado por segmento *bss*, um nome derivado de um antigo mnemônico *assembler* para "block started by symbol".

- **Pilha:** a pilha é um segmento que cresce e encolhe dinamicamente ao se adicionar a remover *stack frames*. Um *stack frame* é alocado para cada chamada de função. Um *frame* armazena as variáveis locais da função (também chamado de variáveis automáticas), parâmetros e valor de retorno.

- **Heap:** A *heap* é uma área em que a memória (para variáveis) pode ser dinamicamente alocada em tempo de execução.

#### 6.1.1. Espaços de endereçamento

Espaços de endereçamento são representações de memória dada para cada processo situado no espaço de usuário no sistema. Cada processo é capaz de enxergar somente o seu espaço de endereçamento, como se toda a memória do sistema pertencesse a ele. Além disso, os espaços de endereçamento podem ser muito maiores do que a memória física disponível. O processo, por meio do *kernel*, pode dinamicamente adicionar e remover áreas de memória de seu espaço de endereçamento.

Cada processo possui um espaço de endereçamento associado, que nada mais é do que uma lista com endereços de memória, indo de 0 até algum valor máximo, no qual o processo pode ler e escrever, respeitando-se as permissões de cada área.

Endereços de memória localizados no espaço de endereçamento de um processo são totalmente

isolados dos mesmos endereços de memória do espaço de endereçamento de um outro processo, salvo casos onde um processo compartilha partes de seu espaço de endereçamento com outro processo. Espaços de endereçamento permitem que a memória dada a um processo esteja isolada dos demais. Diversos processos podem ter dados diferentes no mesmo endereço em seus respectivos espaços de endereçamento, pois estes dados estão disponíveis apenas em seu contexto, e não são visíveis externamente.

As áreas de memória dentro de um espaço de endereçamento possuem algumas permissões associadas: leitura, escrita e execução. Para que o processo possa acessar determinada área, ele deve possuir as permissões necessárias. Um acesso a um endereço de memória em uma área inválida faz com que o processo seja morto pelo kernel, seguido de uma mensagem de "*segmentation fault*".

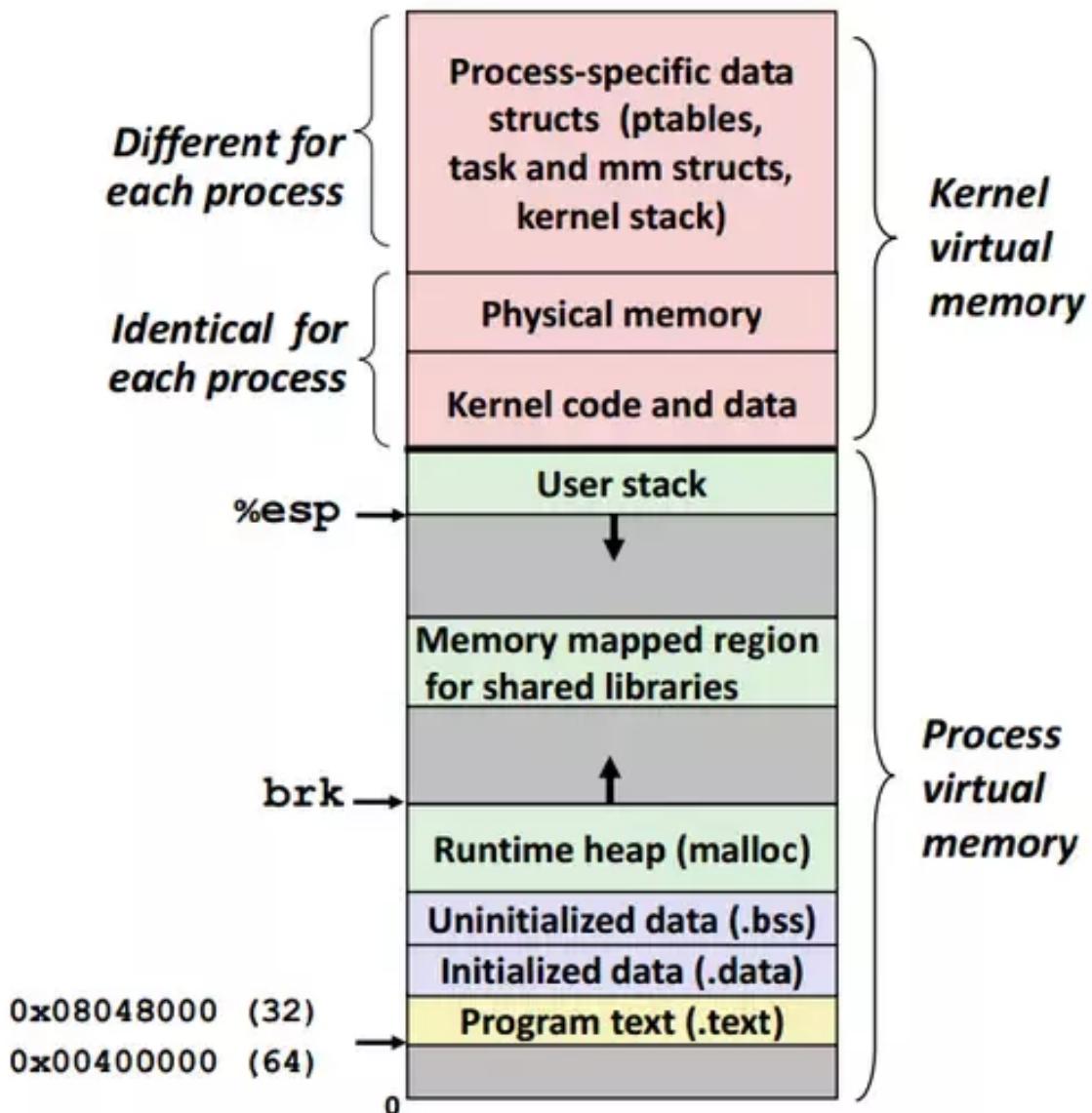

A figura abaixo ilustra o modelo de memória de um processo, sendo representado por seu espaço de endereçamento. Como pode ser observado, o espaço de endereçamento realiza o mapeamento do espaço de memória do *kernel* no topo de seu endereço. Em geral, os sistemas operacionais possuem o *kernel* mapeado no espaço de endereçamento de cada um dos processos. No entanto, este mapeamento não resulta em desperdício de memória, visto que já apenas uma instância do *kernel* alocada na memória física.

## Virtual memory address (hexadecimal)

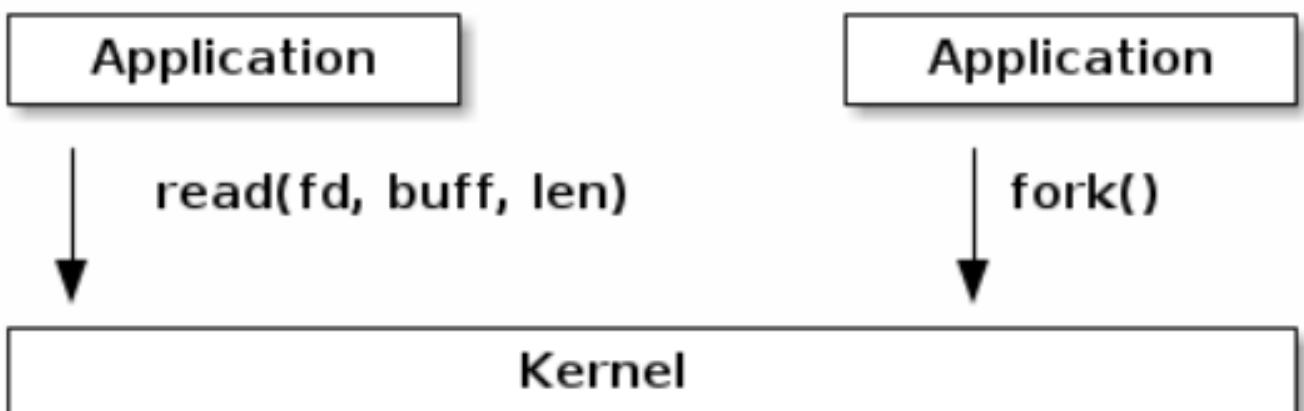

## 6.2. System calls

Quando um programa aplicação deseja utilizar algum recurso do sistema, este deve ser feito por meio das abstrações oferecidas pelos sistemas operacionais. Este processo é realizado utilizando uma *system call*, que nada mais é do que uma função de um tipo especial, no qual o processo entra no modo *kernel*, ou seja, executa funções ligadas ao *kernel* com permissões privilegiadas. De modo geral, fazer uma *system call* é como fazer um tipo especial de chamada de função, só que *system calls* entram no *kernel*, e chamadas comuns, não.

*System calls* proveem uma camada entre o hardware e os processos a nível de usuário. Esta camada

serve para três propósitos principais:

- Primeiro, ela provê uma interface abstrata de hardware para o espaço de usuário. Quando há leitura ou escrita de um arquivo, por exemplo, aplicações não se preocupam com o tipo de disco, mídia ou até mesmo o tipo do sistema de arquivos sob o qual o arquivo reside.

- Segundo, *system calls* garantem a segurança do sistema e sua estabilidade. Com o *kernel* atuando como um intermediário entre os recursos do sistema e o espaço de usuário, o *kernel* pode arbitrar o acesso baseado nas permissões, usuários e outros critérios.

- Por último, uma camada única entre o espaço de usuário e o resto do sistema permite a utilização de uma abstração do sistema real por parte dos processos. Se aplicações fossem livres para acessar os recursos do sistema sem o conhecimento do *kernel*, seria quase impossível implementar mecanismos de *multitasking* e memória virtual, e certamente impossível de fazê-lo com estabilidade e segurança.

### Alguns pontos sobre *system calls*

- Uma *system call* altera o estado do processo de modo usuário para o modo kernel, para que a CPU, executando o processo de usuário, possa acessar a memória protegida do *kernel*.

- O conjunto de *system calls* é fixo. Cada *system call* é identificada por um número único.

- Cada *system call* possui um conjunto de parâmetros que especificam as informações que serão transferidas do modo usuário, ou seja, do espaço de endereçamento do processo, para o espaço do *kernel*, e vice-versa.

A figura abaixo exibe uma representação envolvendo aplicações e *system calls*. Ao executar um *read()*, ou um *fork()*, a aplicação está, na verdade, realizando *system calls* ao *kernel*.

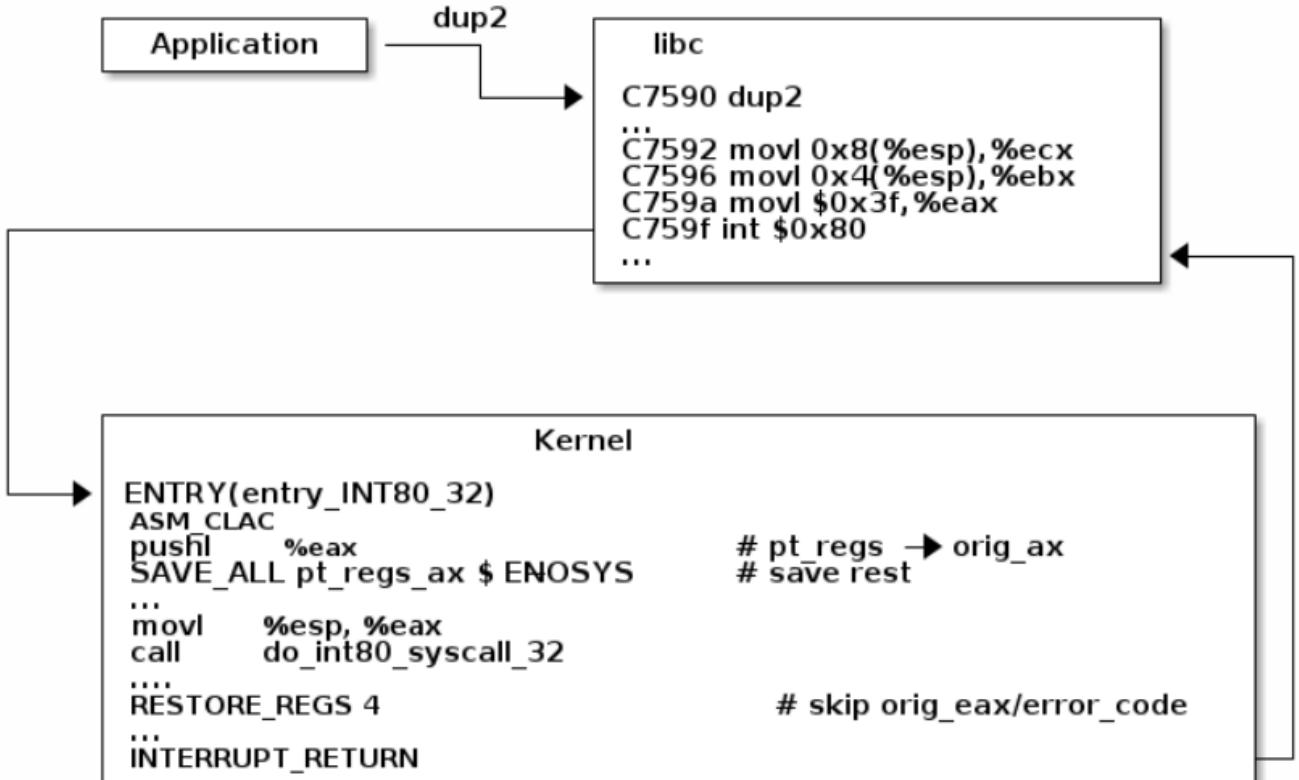

#### 6.2.1. Execução

Para realizar uma *system call* em uma arquitetura x86-32, por exemplo, são executados os seguintes passos:

1. O programa aplicação faz uma *system call* invocando uma função C que serve como um invólucro (uma função da *libc*, por exemplo), que por sua vez chama uma função do *kernel*.

2. Esta função C deve tornar todos os parâmetros da *system call* disponíveis para a rotina que realiza o tratamento da exceção (*trap*) da *system call*. Estes parâmetros são passados para a

função C via uma estrutura de dados de pilha, mas o *kernel* os espera em registradores específicos. A função C, então, copia os argumentos para estes registradores.

- Para o kernel Linux/x86-32, os registradores para a passagem de parâmetros entre o espaço de usuário e o *kernel* estão definidos no arquivo *arch/x86/ia32entry.S*, e são os seguintes:

| Registrador | Descrição                    |

|-------------|------------------------------|

| %eax        | Número da <i>system call</i> |

| %ebx        | Parâmetro 1                  |

| %ecx        | Parâmetro 2                  |

| %edx        | Parâmetro 3                  |

| %esi        | Parâmetro 4                  |

| %edi        | Parâmetro 5                  |

| %ebp        | Parâmetro 6                  |

1. Uma vez que a *system call* entra no modo *kernel*, o *kernel* necessita de algum método para identificar qual é a *system call* que está sendo invocada. Para isso, a função C copia o número da *system call* em um registrador específico da CPU (*eax*).

2. A função C executa uma instrução de máquina (*int 0x80*), o que força o processador a trocar do modo de usuário para o modo *kernel* e executar o código apontado pela localização *0x80* (128, em decimal) do vetor de exceções do sistema.

3. Em resposta à exceção da posição *0x80*, o *kernel* invoca sua rotina *system\_call()* (localizada no arquivo *assembly arch/i386/entry.S*, no *kernel* Linux) para lidar com a exceção. Este *handler*:

1. Salva os valores dos registradores na pilha do *kernel*.

2. Verifica a validade do número da *system call*.

3. Invoca a rotina apropriada para a *system call*, a qual é encontrada utilizando o número da *system call* como índice em uma tabela que contém todas as rotinas de *system calls* (no *kernel* Linux, é a variável *sys\_call\_table*). Se a rotina de serviço da *system call* possuir algum parâmetro, primeiro ele verifica a sua validade (por exemplo, é verificado se o endereço aponta para posições válidas na memória de usuário). Então a rotina de serviço executa a tarefa requisitada, o que pode envolver a modificação de valores nos endereços especificados nos parâmetros recebidos e também a transferência de dados entre memória de usuário e memória do *kernel* (operações de I/O). Por fim, a rotina de serviço retorna o estado do resultado por meio da chamada *system\_call()*.

4. Restaura os valores dos registradores da pilha do *kernel* e coloca o valor de retorno da *system call* na pilha.

5. Retorna para a função C, ao mesmo tempo que retorna o processador para o modo usuário, utilizando a instrução *iret*.

4. Se o valor de retorno da rotina de serviço da *system call* sinalizar algum erro, a função C atribui o valor recebido à variável global *errno*. A função C então retorna para quem a chamou, fornecendo um número inteiro como retorno, indicando o sucesso/falha da *system call*.

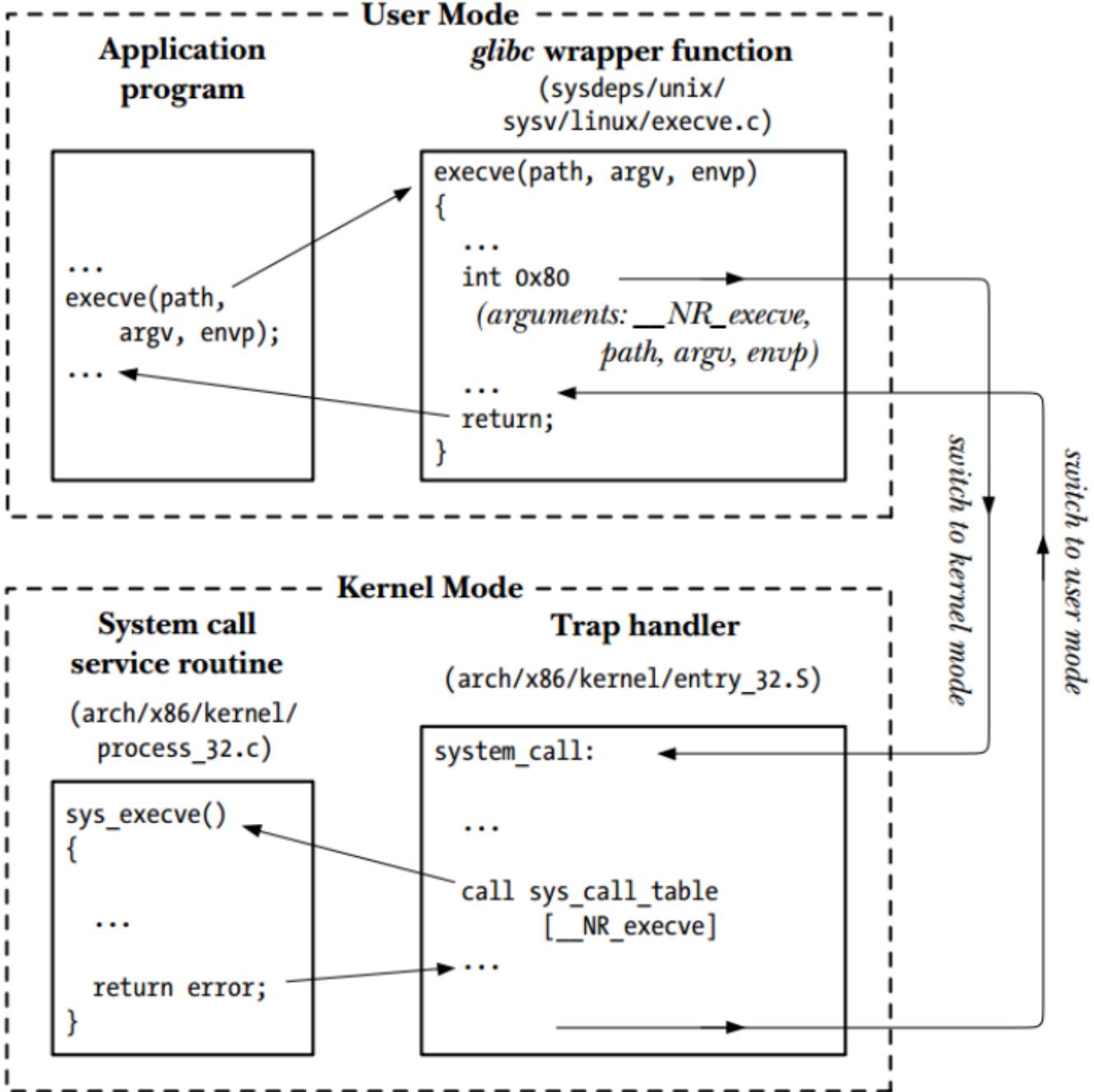

A figura abaixo apresenta uma visão geral dos passos mencionados acima. Uma aplicação, ao chamar uma função da *libc*, está, na verdade, invocando uma *system call* ao *kernel*. A função da *libc* prepara os parâmetros que serão enviados ao *kernel* e, ao fim do processo, prepara o retorno que será dado ao processo do usuário.

### 6.2.2. Exemplo

A figura abaixo apresenta a sequência explicitada acima, usando o exemplo da *system call execve()*. No Linux/x86-32, *execve()* é a *system call* número 11 (*\_NR\_execve*). Portanto, no vetor *sys\_call\_table*, a entrada 11 contém o endereço de *sys\_execve()*, a rotina de serviço para esta *system call*. No Linux, rotinas de serviço de *system calls* geralmente têm nomes na forma *sys\_xyz()*, onde *xyz* é o nome da "system call" em questão.

Versões mais recentes da arquitetura x86-32 implementam as instruções `sysenter` e `sysexit`, as quais proveem um método para entrar e sair do modo *kernel* mais rápido do que a instrução `int 0x80` convencional. O uso destas novas instruções são suportadas pela versão 2.6 do *kernel* do Linux, e para as versões 2.3.2 ou maiores do *glibc*.

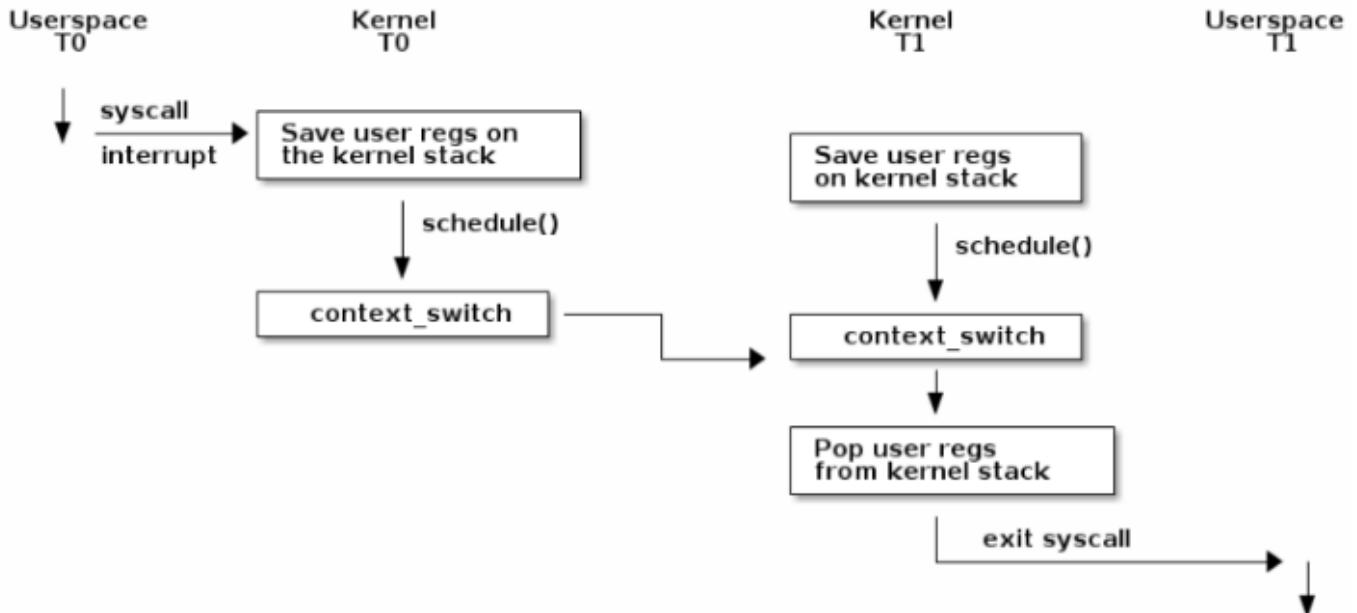

### 6.3. Switch context

A figura abaixo exibe uma visão geral do procedimento da troca de contexto em um kernel Linux. A thread **T0** realiza uma operação de *I/O* no disco. Antes que uma troca de contexto possa ocorrer, é necessário realizar um chaveamento para o modo *kernel*. Neste ponto, os registradores do espaço de usuário são salvos na pilha do *kernel*, assunto que será visto mais adiante. Em algum momento, a função `schedule()` é chamada para decidir que uma troca de contexto deve ocorrer de **T0** para **T1**, pois **T0** está bloqueada esperando a operação de *I/O* completar.

### 6.3.1. Principais causas para a troca de contexto entre processos

- **Multitasking**

É muito comum a utilização de algoritmos de escalonamento para dividir o tempo de CPU entre diversos processos, escolhendo quais processos devem executar e se o processo atual deve interromper o seu processamento para que outro processo tome o seu lugar. Retirar um processo da CPU envolve a troca de contexto entre processos, e ela pode ser disparada porque o processo tornou-se inapto a executar, talvez porque esteja esperando por uma operação de *I/O*, ou então a finalização de uma operação de sincronização.

Em um sistema *multitasking* preemptivo, o escalonador também deve trocar processos que estão executando e poderiam continuar executando por mais algum tempo. Para garantir que o tempo de CPU seja dividido justamente entre todos os processos, escalonadores preemptivos frequentemente configuram uma interrupção de *timer*, que dispara sempre que um processo excede a sua quantidade de tempo. Esta interrupção garante que o escalonador ganhe o controle da CPU e realize uma troca de contexto.

- **Interrupções**

Arquiteturas modernas são guiadas por interrupções. Isso significa que, se a CPU realiza uma requisição para recuperar dados de um disco, por exemplo, ela não precisa realizar uma operação de *busy wait* até que a leitura complete; ela pode simplesmente iniciar a requisição (para o dispositivo de *I/O*) e realizar alguma outra tarefa até que a resposta retorne. Quando a leitura é finalizada, a CPU é interrompida e recebe resultado da leitura. Para isso, um programa chamado **tratador de interrupções** (*interrupt handler*) é utilizado.

Quando uma interrupção ocorre, o hardware automaticamente troca uma parte do contexto, deixando ao menos o necessário para permitir ao tratador de interrupções retornar ao código interrompido. O tratador pode salvar contextos adicionais, dependendo dos detalhes do hardware em particular e do projeto de software. Frequentemente, somente uma parte mínima do contexto é trocada a fim de minimizar a quantidade de tempo gasto tratando a interrupção. O *kernel* não invoca ou escalona um processo especial para lidar com as interrupções mas, em vez disso, o tratador de interrupções é executado, geralmente de maneira parcial, no contexto estabelecido no início do tratamento da interrupção. Uma vez que o serviço de interrupção está completo, o contexto anterior à interrupção é restaurado para que o processo interrompido possa retomar a execução.

## 6.4. Kernel space

A troca de contexto entre threads de um mesmo processo requer apenas o salvamento dos registradores utilizados pela *thread* anterior. Devido ao fato de que as threads compartilham dos mesmos recursos, esta tarefa é relativamente simples. Porém, quando a troca de contexto envolve processos diferentes, são necessários alguns passos a mais para que o contexto do processo anterior seja salvo antes que a CPU possa carregar o contexto do próximo processo.

A troca de contexto entre dois processos exige que o espaço de endereçamento do primeiro seja devidamente salvo, e que o espaço de endereçamento do segundo processo seja carregado.

No entanto, considerando as plataformas de computação atuais, em que processadores *multicores* são capazes de executar diversas aplicações simultaneamente, é comum o cenário onde vários processos realizam *system calls* ao *kernel* e logo em seguida sofram preempção, antes mesmo de receber a resposta da *system call*. Para lidar com estes casos, os serviços do *kernel* são projetados para serem reentrantes, permitindo que múltiplos processos entrem no espaço do *kernel* e utilizem estes serviços. Para realizar o controle de quais processos estão executando quais *system calls*, e quais são os seus contextos dentro do *kernel*, cada processo recebe sua própria pilha de *kernel* privada, com o objetivo de manter os dados de chamadas de funções, armazenar dados locais das funções de *kernel*, entre outros usos.

Na imagem abaixo podemos ver a estrutura geral da memória de um processo. A parte mais alta exibe a memória virtual do *kernel*, que possui uma parte que é idêntica para cada processo, envolvendo dados e código do *kernel*, e outra parte que é diferente para cada processo, e é nesta área onde são armazenados os dados específicos de cada processo relacionados ao *kernel*, como *ptables* e as pilhas de *kernel*, por exemplo. Embora a memória do *kernel* esteja no espaço de endereçamento do processo, ela é uma área protegida e o processo não pode acessá-la diretamente.

Como foi visto na figura anterior, o *kernel* é mapeado no espaço de endereçamento de cada processo. Dentro do espaço utilizado pelo *kernel* há uma pilha especial para cada processo. A representação desta pilha é apresentada na figura abaixo. No kernel do Linux, cada pilha contém as informações do processo associado, representado pela *struct thread\_info*, a qual armazena informações sobre o descritor do processo.

A pilha do kernel está diretamente mapeada à memória física, obrigando que os endereços estejam dispostos fisicamente em uma região contígua de memória. Para sistemas x86-32, a pilha do kernel possui, por padrão, 8 KB de tamanho, sendo possível configurá-la para tamanhos de 4 KB (durante a build do *kernel*) e 16 KB (para sistemas x86-64).

## 6.5. Referências

TANENBAUM, Andrew S., BOS, Herbert. **Modern Operating Systems**. Fourth edition, 2015. Pearson.

LOVE, Robert. **Linux Kernel Development - A thorough guide to the design and**

**implementation of the Linux kernel.** Third edition. Developer's Library.

The Linux Kernel, 5.10.14. **System Calls - Linux system calls implementation.** Disponível em: <<https://linux-kernel-labs.github.io/refs/heads/master/lectures/syscalls.html>>. Acesso em: 26 de julho de 2021.

KERRISK, Michael. **The Linux Programming Interface - A Linux and UNIX System Programming Handbook.** no starch press, San Francisco.

BHARADWAJ, Raghu. **Mastering Linux Kernel Development: A Kernel Developer's Reference Manual.** Packt Publishing.

## 7. MMU for Paging

### 7.1. Conceitos importantes

A seguir são definidos alguns conceitos importantes para o entendimento dos conceitos de MMU e Paging:

- **Virtual Address** - O endereço usado pelo processador (pela aplicação em execução). O Stack Pointer, Instruction Counter e registradores de retorno usam endereços virtuais. Esses endereços não necessariamente são únicos, e do ponto de vista do programador, os endereços vão de 0 até o valor definido como tamanho máximo do espaço de endereçamento da aplicação. Portanto, dois programas rodando em um mesmo sistema podem por exemplo apontar para o mesmo endereço virtual, mas que na memória física são completamente diferentes.

- **Physical Address** - Endereço na memória principal (RAM), tido a partir do processo de tradução do endereço virtual para determinada aplicação.

- **Page/Section** - Uma página(Page) é um espaço de endereçamento na memória da aplicação com tamanho definido pela arquitetura. Páginas de memória de um programa não necessariamente estão carregadas na memória RAM, e podem estar armazenadas no disco, por exemplo. Páginas são carregadas pelo sistema operacional de acordo com a necessidade e o espaço disponível. Quando uma página da memória virtual é carregada para a memória RAM, ela é disposta em um frame da memória física. A memória física é dividida em frames. Seções(Sections) são semelhantes a páginas, porém maiores.

- **Page Frame** - Espaço na memória física do tamanho de uma página. A memória física contém um determinado número de frames de um tamanho pré definido pela arquitetura.

- **Page Table/Page Directory** - Um vetor de registros usados para tradução de endereços virtuais para físicos. Para cada programa há uma tabela de páginas(Page tables). As tabelas de páginas primárias(aquelas pelas quais o processo de tradução de endereço se inicia) podem ser chamadas de tabelas de diretório(Page directory).

- **ASID(Address Space Identifier)** - Identificador do espaço de armazenamento.

- **TLB(Table Lookahead Buffer)**-Buffer com os últimos endereços virtuais traduzidos. É mantido pela MMU.

### 7.2. MMU

A MMU é um componente de hardware responsável por realizar a tradução de endereços virtuais para endereços físicos quando a paginação está habilitada. Todos os endereços físicos absolutos são

calculados com base nas entradas definidas na tabela de diretório; esse comportamento restringe os endereços alcançáveis para aqueles mapeados na tabela de diretório de um processo. Podem existir diferentes tabelas de diretório, o que torna possível limitar o acesso de diferentes processos a diferentes segmentos de memória. Essa restrição também pode levar em consideração aspectos como o modo em que o processador está operando ou o tratamento de exceções.

### 7.3. Paging

O conceito de paginação dentro de sistemas operacionais é fortemente atrelado à ideia de memória virtual. Em um sistema sem memória virtual, os endereços de memória referenciados pelo programa em execução no processador são exatamente os endereços da memória principal que se pretende acessar. Isso implica que a memória endereçável pelo processador se limita ao tamanho da memória. Em um sistema com endereçamento virtual, cada programa tem um espaço de endereçamento próprio, que vai de 0 até um tamanho definido pelo sistema operacional. Cada programa também detém uma Page Table, que é usada para mapear os endereços virtuais utilizados pelo programa para endereços físicos. Cada entrada da tabela de páginas contém ou um endereço físico para onde o endereço virtual está mapeado, ou um indicador de que aquela página não está na memória principal (de rápido acesso), e precisa ser carregada da memória secundária (significativamente mais lenta).

Dessa forma, para um programa executar, não é necessário que todos os dados deste estejam em memória de forma contínua (tanto em espaço quanto em tempo). O programa tem acesso ao espaço de endereçamento máximo possibilitado pela arquitetura, e não é limitado pela memória primária (RAM) instalada. Por exemplo, um programa executando em uma arquitetura de 32 bits, terá acesso a um espaço de endereçamento de  $2^{32}$  bytes (4GB), mesmo que a máquina tenha apenas 1GB de memória RAM instalada.

Dentro da arquitetura do EPOS, a abstração da MMU é feita pela classe `MMU_Common`, que é especializada para cada arquitetura-alvo. Essa classe leva é parametrizada (ela é um template) com os valores para `DIRECTORY_BITS`, `PAGE_BITS`, `OFFSET_BITS` que definem quantos bits dos endereços são usados para cada parte da tradução. O `DIRECTORY_BITS` indica o número de bits utilizados para acessar a tabela de diretório, `PAGE_BITS` para a tabela de paginação e `OFFSET_BITS` é concatenado diretamente ao final da tradução para completar o endereço físico, e basicamente move o acesso a memória dentro de uma página específica. O tamanho das páginas dentro do EPOS é dado por 2 elevado ao valor de `PAGE_BITS`.

### 7.4. MMU - ARMv7

Além das funcionalidades básicas conceitualmente atribuídas a uma MMU, a VMSA (Virtual Memory

System Architecture) do ARMv7 possui extensões que alteram o funcionamento do endereçamento virtual. Com base no escopo dos próximos entregáveis serão brevemente apresentadas apenas 3: Security Extensions, Virtualization e Large Physical Address.

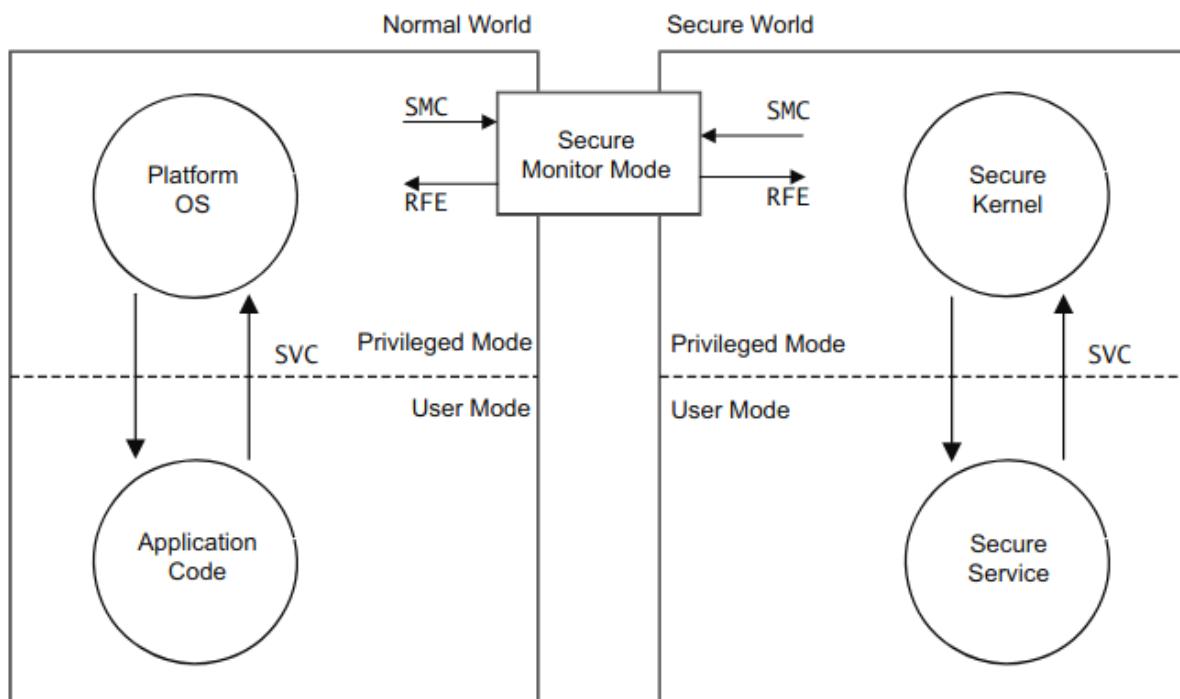

Security extensions, também referenciada como TrustZone, provê a possibilidade de separar código e dados considerados sensíveis ao isolá-los em uma região da memória chamada de secure world. Utilizando essa extensão o hardware garante que nenhum recurso presente no secure world seja acessível do normal world (local onde as aplicações consideradas não seguras serão salvas e executadas); ao habilitar essa extensão um novo bit (o bit NS) é adicionado à todas as transações que envolvem acesso a memória, tornando possível a divisão da memória entre as aplicações do normal world e secure world.

Por fim, é possível que qualquer core execute código referente a qualquer um dos modos; para tal é utilizado um novo modo: o monitor mode; é através dele que quaisquer modificações necessárias no sistema para execução de códigos de níveis diferentes é feita.

Virtualization é uma extensão da VMSA que possibilita aos processadores o acesso a um novo modo, o hypervisor mode; esse modo possui um nível de privilégio maior do que os níveis de privilégio padrões do ARMv7. Os softwares de virtualização, chamados hypervisors, utilizarão esse método para gerenciar a execução dos múltiplos sistemas operacionais em execução.

Essa extensão se relaciona a VMSA devido ao fato de seu suporte implicar na necessidade de um espaço de endereçamento maior (uso da extensão large physical address) e alteração no funcionamento de tradução de endereços virtuais. Tais tópicos não serão desenvolvidos devido a complexidade e falta de relação com a idéia principal de paginação.

A última extensão, Large Physical Address, aumenta a faixa de endereços físicos endereçáveis de 4GB para 1TB. Em termos de MMU essa extensão adiciona um nível a mais no processo de tradução de endereços virtuais, mantendo os endereços virtuais com 32 bits. Como citado anteriormente essa extensão é necessária para que possa ocorrer virtualização.

## 7.5. Paging - ARMv7

A VMSA do ARMv7 possui quatro esquemas de paginação padrão. A diversidade de esquemas torna possível explorar as necessidades específicas das aplicações que serão executadas e levá-las em consideração na hora de configurar a MMU. A principal diferença entre os quatro esquemas é a unidade de fragmentação da memória. Os esquemas que utilizam Sections (seções) dividem a

memória em fragmentos maiores, enquanto os esquemas que utilizam páginas usam valores menores. A seguir serão apresentados os quatro esquemas e o significado de cada campo do endereço virtual para cada um deles.

### 7.5.1. Super Section

Esquema de endereçamento virtual de 1 nível. Ou seja, ao adotar esse modelo os processos necessitam de apenas uma tabela de páginas para traduzir seus endereços virtuais. Nesse esquema a unidade de fragmentação de memória são as Super Sections(também é possível imaginar as Super Sections como páginas), fragmentos de memória física de 16MB. Os significados de cada campo dos endereços virtuais mediante esse esquema são descritos abaixo.

### 7.5.2. Section

Esquema de endereçamento virtual de 1 nível. Ou seja, ao adotar esse modelo os processos necessitam de apenas uma tabela de páginas para traduzir seus endereços virtuais. Nesse esquema a unidade de fragmentação de memória são as Sections(também é possível imaginar as Sections como páginas), fragmentos de memória física de 1MB. Os significados de cada campo dos endereços virtuais mediante esse esquema são descritos abaixo.

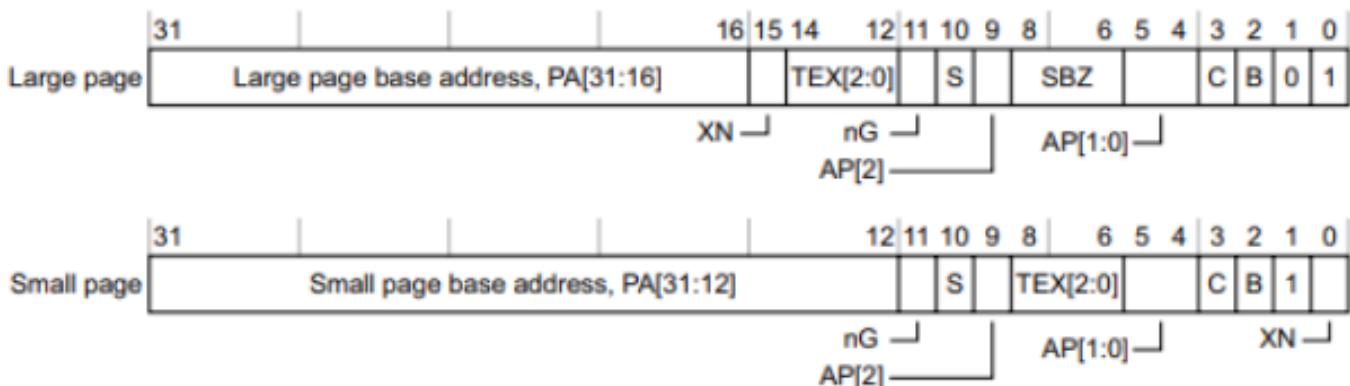

### 7.5.3. Large Page

Esquema de endereçamento virtual de 2 níveis. Ou seja, ao adotar esse modelo os processos necessitam de percorrer duas tabelas de páginas para traduzir seus endereços virtuais. Nesse esquema a unidade de fragmentação de memória são as Large Pages(também é possível imaginar as Large Pages como páginas), fragmentos de memória física de 64KB. Os significados de cada campo dos endereços virtuais mediante esse esquema são descritos abaixo.

Exemplo endereço virtual

| bits:  | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| valor: | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 0  |

Offset na tabela de pag primária      Offset na tabela de pág secundária      Offset na large page(página de 64KB)

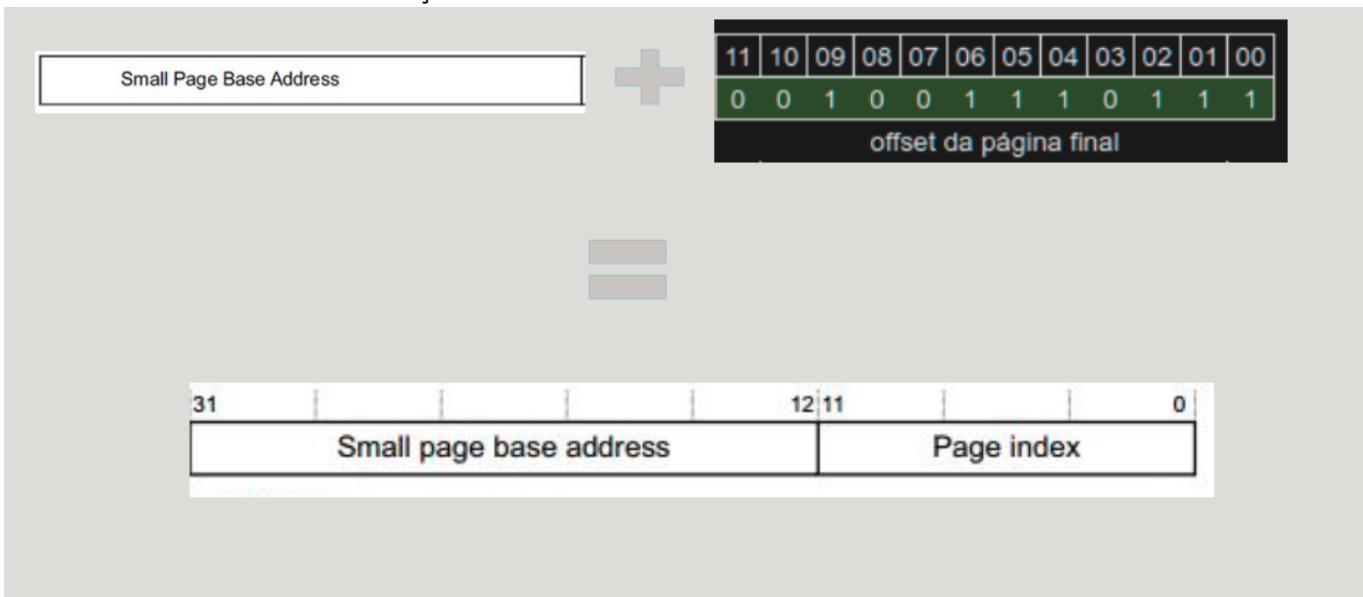

#### 7.5.4. Small Page

Esquema de endereçamento virtual de 2 níveis. Ou seja, ao adotar esse modelo os processos necessitam de percorrer duas tabelas de páginas para traduzir seus endereços virtuais. Nesse esquema a unidade de fragmentação de memória são as Small Pages(também é possível imaginar as

Small Pages como páginas), fragmentos de memória física de 4KB. Os significados de cada campo dos endereços virtuais mediante esse esquema são descritos abaixo.

| Exemplo end virtual |                                |    |    |    |    |    |    |    |    |    |    |                               |    |    |    |    |    |    |    |    |    |    |                        |    |    |    |    |    |    |    |    |    |   |

|---------------------|--------------------------------|----|----|----|----|----|----|----|----|----|----|-------------------------------|----|----|----|----|----|----|----|----|----|----|------------------------|----|----|----|----|----|----|----|----|----|---|

| bits:               | 31                             | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20                            | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 09                     | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |   |

| valor:              | 1                              | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0                             | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0                      | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 1 |

|                     | offset na tabela de pags prim. |    |    |    |    |    |    |    |    |    |    | offset na tabela de pags sec. |    |    |    |    |    |    |    |    |    |    | offset da página final |    |    |    |    |    |    |    |    |    |   |

## 7.6. Exemplo de tradução de endereço no ARMv7

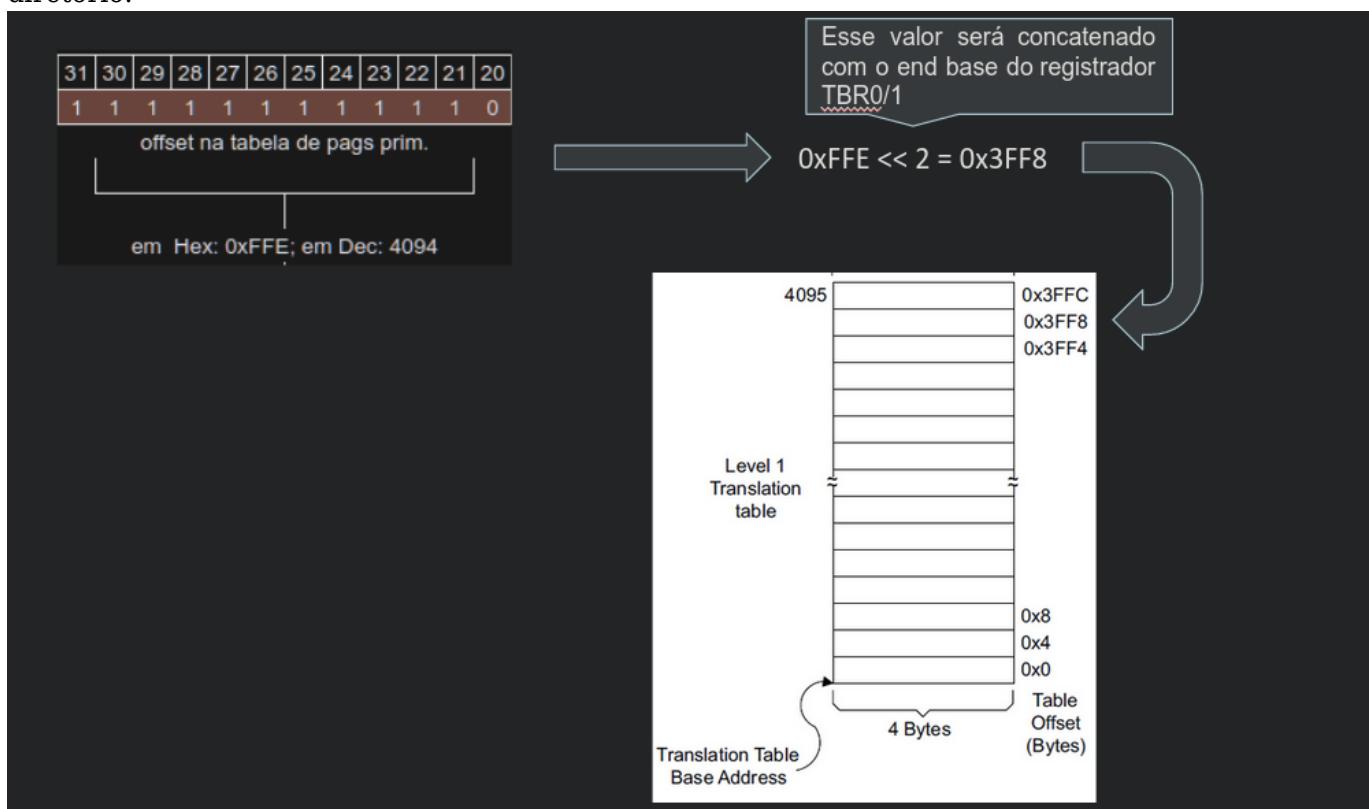

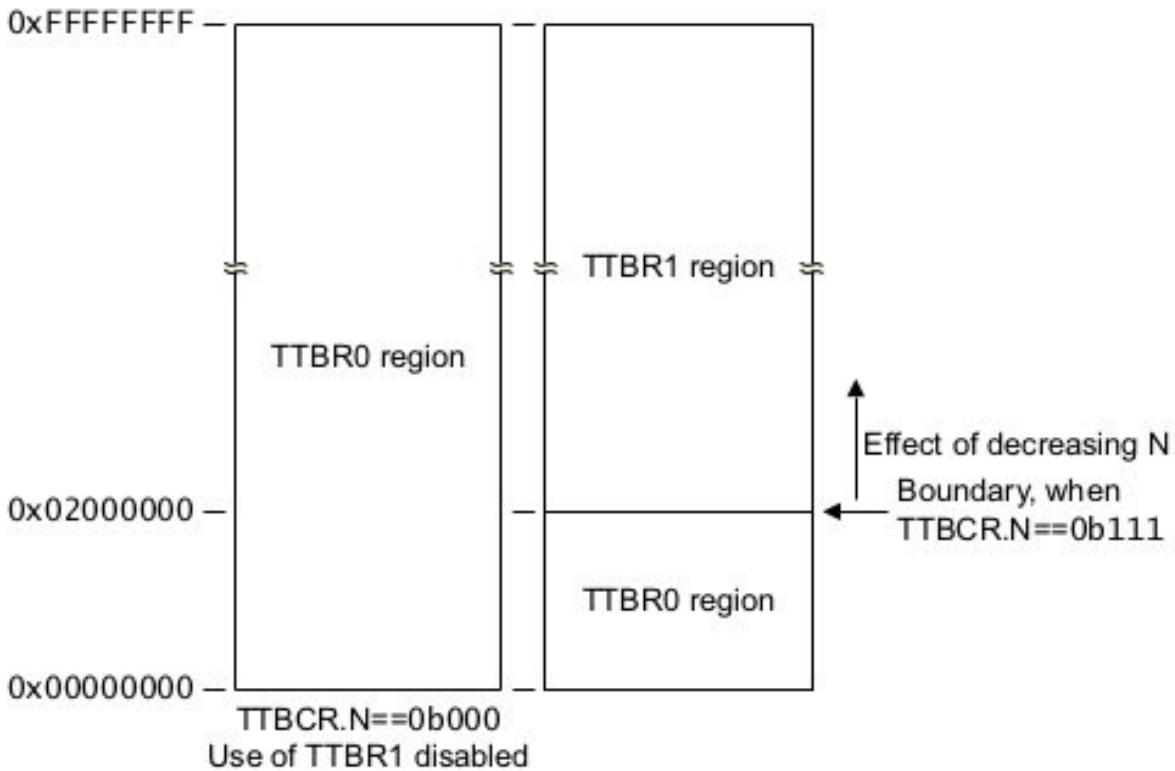

Supondo o uso de páginas de 4KB(small pages) e N = 1 e que a consulta a TLB não obteve sucesso, a tradução de endereço se dá por:

- É selecionado o endereço base da tabela de diretório a ser consultado usando os bits 31-14 do TTBR0, ou TTBR1 se o endereço for igual ou maior do que 0x8000000.

- Os bits 31-20 são concatenados ao endereço base da tabela de diretório. O resultado é deslocado 2 bits para a esquerda, formando um endereço de 32 bits que aponta para uma entrada na tabela de diretório.

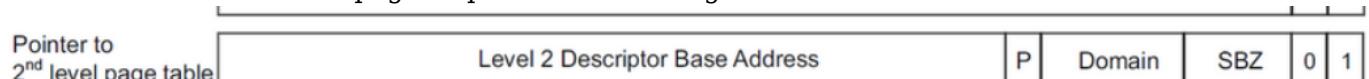

- A entrada da tabela de páginas primária tem a seguinte estrutura:

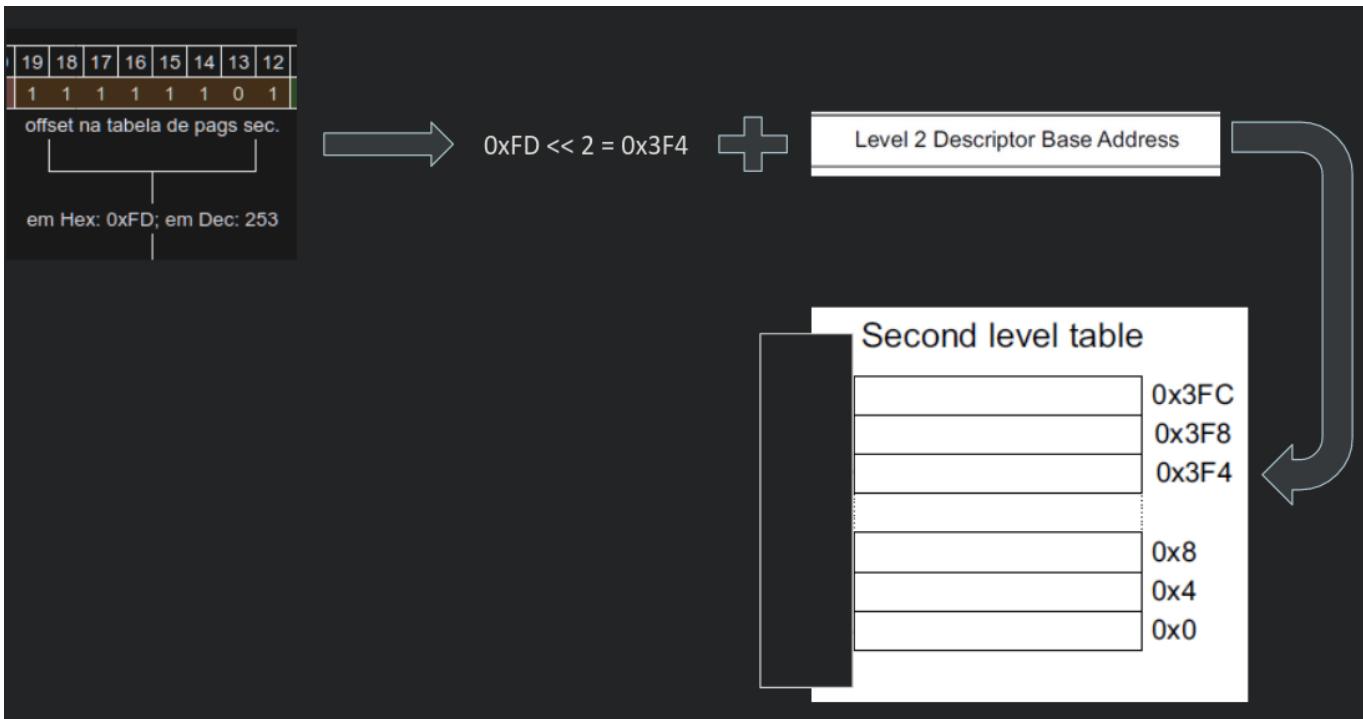

- Os bits 31-10 do valor no endereço formado são concatenados aos bits 19-12 do endereço de entrada; o resultado é descolado 2 bits para a esquerda;

5. O endereço formado é usado para acessar uma entrada específica na tabela de páginas secundária apontada pela entrada do item 3.

Se a entrada for válida (bit na posição 1 igual a 1), ou seja, estiver na memória principal, os bits **31-12** do valor no endereço são concatenados aos bits **11-0** do endereço de entrada (bits de offset), e o valor resultante é um endereço físico na memória.

## 7.7. Ativação da MMU no ARMv7

Abaixo segue um exemplo de ativação da MMU. A implementação não segue as definições da arquitetura do EPOS para simplificar, porém utiliza alguns termos dela para facilitar a conexão com ela. As constantes PD\_ENTRIES, PT\_ENTRIES, DIRECTORY\_BITS e PAGE\_BITS são definidas na classe MMU\_Common do EPOS, por exemplo. As estruturas Page\_Directory e Page\_Table também existem na classe MMU\_ARMv7, porém são classes mais complexas. Os mecanismos usados para garantir o alinhamento em memória dos endereços das estruturas também são outros, porém no exemplo é utilizado um alocador específico.

```

struct Page_Directory { PD_Entry entries[PD_ENTRIES]; }; struct Page_Table { PT_Entry

entries[PT_ENTRIES]; }; void* pd_address = aligned_alloc(0x1 << 14, sizeof(Page_Directory));

Page_Directory* page_dir = reinterpret_cast<Page_Directory*> pd_address; // Para cada tabela

de páginas de segundo nível, é necessário alocar o espaço // e apontar elas em cada linha da

Page_Directory. O alinhamento de cada // tabela de páginas precisa ser alinhada em

PAGE_OFFSET, ou seja, 12 bits // ou 0x1 << PAGE_OFFSET // Faz setup do TTBCR, com N = 0

uint32_t ttbcr; // Carrega o valor atual do registrador __asm__ __volatile__ ("mrc p15, 0, %r, c2,

c0, 2" : "=r"(ttbcr) :); // Zera os 3 últimos bits (N), indicando uso apenas do TTBR0 ttbcr &=

0xFFFFFFFF8; // Escreve de volta __asm__ __volatile__ ("mcr p15, 0, %r, c2, c0, 2" : : "r"(ttbcr)); //

Carrega o endereço base do diretório (page table de primeiro nível) uint32_t ttbr0; // Carrega o

ttbr0 existente __asm__ __volatile__ ("mrc p15, 0, %r, c2, c0, 0" : "=r"(ttbr0) :); // Aplica máscara

0b 0000 0000 0000 0000 0011 1111 1111 // Zera os bits [31-14], já que N=0 ttbr0 &=

0x000003FF; // Preenche os bits [31-14] com endereço alinhado alocado anteriormente ttbr0 +=

pd_address // Escreve de volta __asm__ __volatile__ ("mcr p15, 0, %r, c2, c0, 0" : : "r"(ttbr0)); //

Por fim, ativa a MMU setando o bit M do registrador de controle // SCTLR (System Control

Register) CRn = c1, Op1 = 0, CRm = c0, Op2 = 0 __asm__ __volatile__ ("mrc p15, 0, r1, c1, c0, 0

;Read control register \n" "orr R1, #0x1 ;Set M bit \n" "mcr p15, 0, r1, c1, c0, 0 ;Write control

register and enable MMU \n");

```

## 7.8. Referências

Acesso a registradores:

- <https://developer.arm.com/documentation/100511/0401/system-control/register-summary/cp15-system-control-registers-grouped-by-crn-order>

Assembler guide:

- [https://www.keil.com/support/man/docs/armasm/armasm\\_dom1361289850039.htm](https://www.keil.com/support/man/docs/armasm/armasm_dom1361289850039.htm)

Funcionamento da paginação e memória virtual:

- [https://www.youtube.com/watch?v=qcBIvnQt0Bw&list=PLiwt1iVUib9s2Uo5BeYmwkDFUh70fJPxX&index=1&ab\\_channel=DavidBlack-Schaffer](https://www.youtube.com/watch?v=qcBIvnQt0Bw&list=PLiwt1iVUib9s2Uo5BeYmwkDFUh70fJPxX&index=1&ab_channel=DavidBlack-Schaffer)

- [https://www.youtube.com/watch?v=zP4tBRpK3iM&ab\\_channel=MallikarjunK](https://www.youtube.com/watch?v=zP4tBRpK3iM&ab_channel=MallikarjunK)

- <https://sudonull.com/post/11570-Virtual-memory-in-ARMv7>

Noções gerais do processador e uso dos registradores:

- [https://moodle.ufsc.br/pluginfile.php/4417210/mod\\_resource/content/1/DEN0013D\\_cortex\\_a\\_series\\_PG.pdf](https://moodle.ufsc.br/pluginfile.php/4417210/mod_resource/content/1/DEN0013D_cortex_a_series_PG.pdf)

## 8. Task Context Switching

### 8.1. What is Context Switching

Context Switching is the saving and restoring of computational state when switching between different threads or processes, known as tasks. This is an essential feature of a multitasking

operating system so that a task can be restored and resume execution at a later point. This allows multiple processes to share a single central processing unit (CPU).

There are multiple cases where context switching may occur:

- In a multitasking context, it refers to the action of storing the system state for one task, so that one task can be paused and another task resumed.

- A context switch can also occur as the result of an interrupt, such as when a task needs to access disk storage, freeing up CPU time for other tasks.

- Some operating systems also require a context switch to move between user mode and kernel mode tasks.

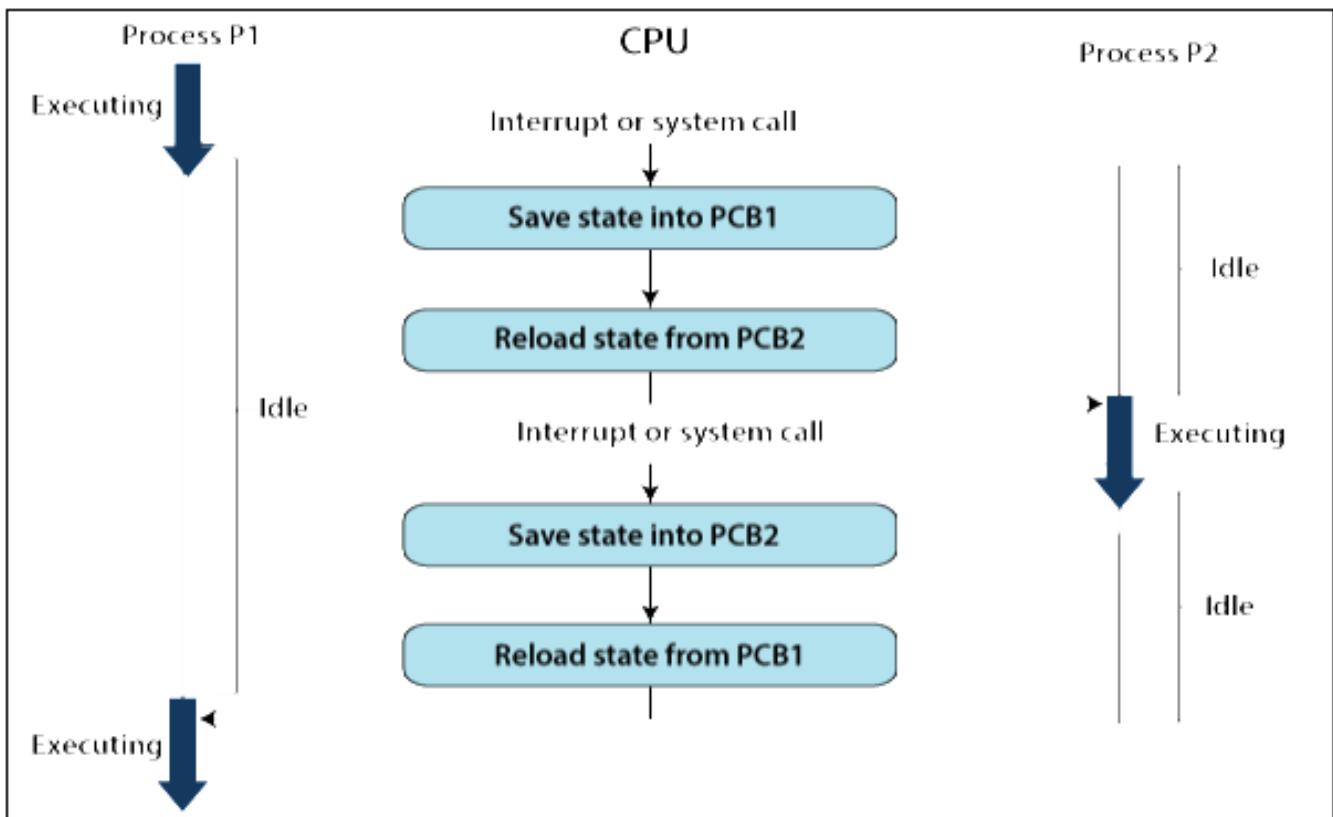

## 8.2. How does a Context Switching happen

In the figure above, you can see that initially process P1 is in running state and process P2 is in ready state. Now, when an interruption occurs and calls for a context switch, you should switch process P1 from running state to ready state after saving the context, and then switch process P2 from ready state to running state. The following steps will be performed:

1. First, the context of process P1, that is, the process present in the execution state, will be saved in the Process Control Block of process P1, that is, PCB1.

2. Now, you must move PCB1 to the relevant queue, i.e., ready queue, I/O queue, waiting queue, etc.

3. In the ready state, select the new process that should be executed, i.e. process, P2.

4. Now update the Process Control Block of process P2, ie PCB2, setting the process state to run. If process P2 was previously executed by the CPU, you can get the position of the last instruction executed so that it can resume execution of P2.

5. Likewise, if you want to run process P1 again, you must follow the same steps mentioned above (from step 1 to 4).

Context switching is used to achieve multitasking, that is, time-sharing multiprogramming. Multitasking gives users the illusion that more than one process is running at the same time. But, in reality, only one task is being performed at any given time by a processor. Here, context switching is so fast that the user feels that the CPU is performing more than one task at the same time.

### 8.3. What is a PCB

A process control block (PCB) is a data structure used by computer operating systems to store all information about a process. It is also known as a process descriptor. When a process is created (started or installed), the operating system creates a corresponding process control block.

**Process-Id**

**Process state**

**Process Priority**

**Accounting

Information**

**Program Counter**

**CPU Register**

**PCB Pointers**

.....

**Process Control Block**

The figure above shows the main information that a PCB may include in its structure. While the details of these structures are system dependent, the common elements fall into three main categories:

- Process identification

- Process state

- Process control

Process identification data includes a unique identifier for the process (almost invariably an integer) and, in a multi-role-multitasking system, data such as parent process identifier, user identifier, user group identifier, etc. The process ID is particularly relevant as it is often used to cross-reference the definitions defined above, for example to show which process is using which I/O devices or memory areas.

The defined process state data or status of a process when it is suspended, allowing the operating system to restart later. This always includes the contents of general purpose CPU registers, a CPU process status word, stack and frame pointers, and so on. During a context switch, the running process is stopped and another process is completed. The kernel must stop an execution of the running process, copy the values from the hardware registers to its PCB, and update the hardware registers with the values from the PCB of the new process.

Process control information is used by the operating system to manage the process itself. That includes:

- Process scheduling state - The state of the process in terms of "ready", "suspended", etc., and also other scheduling information such as priority value, the amount of time elapsed since the process gained control of the CPU or since it was suspended. Also, in case of a suspended process, event identification data must be recorded for the event that the process is waiting for.

- Process structuring information - the child ids of the process, or the ids of other processes related to the current in some functional way, which can be represented as a queue, ring, or other data structures

- Inter-process communication information - flags, signals and messages associated with communication between independent processes

- Process privileges - allowed / not allowed access to system resources

- Process number (PID) - unique identification number for each process (also known as process ID)

- Program counter (PC) - A pointer to the address of the next instruction to be executed for this process

- CPU registers - set of registers where the process needs to be stored for execution to the execution state

- CPU Schedule Information - CPU Time Schedule Information

- Memory Management Information - Page Table, Memory Limits, Segment Table

- Accounting information - amount of CPU used for the execution process, time limits, execution ID, etc.

- I/O status information - list of I/O devices allocated to the process.

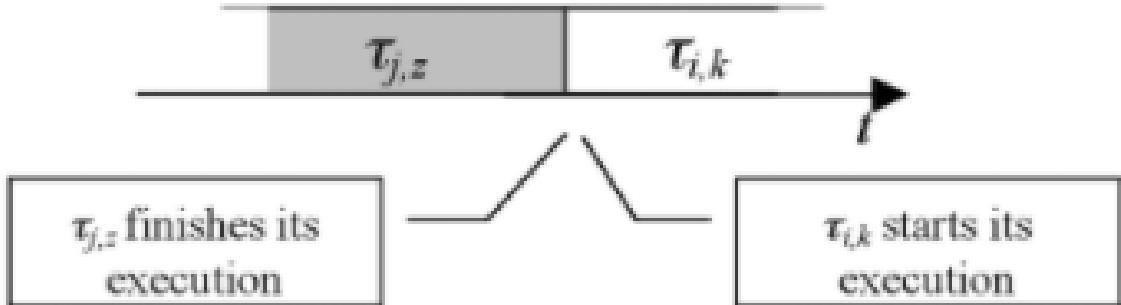

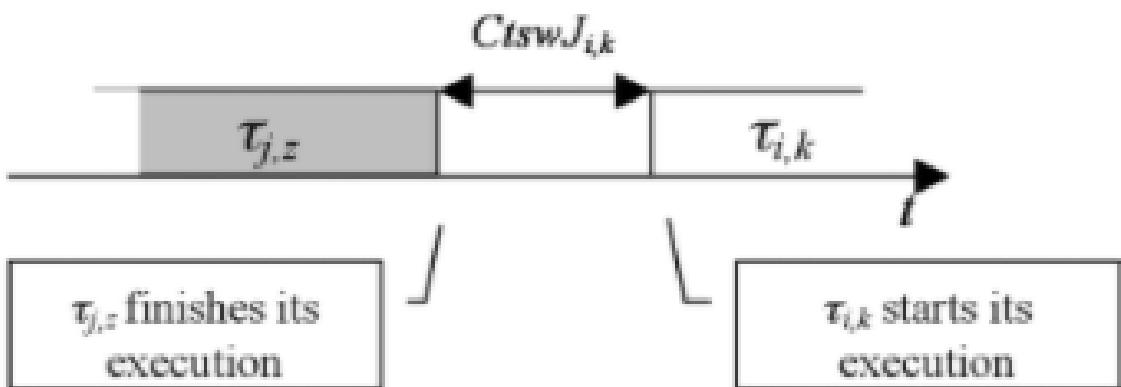

## 8.4. Performance considerations

Context switching involves costs that may affect the system's overall performance. These direct costs arise mainly from the fact that it takes time to save the context of a process that is running and then restore the context of another process that is about to run. During this time, there is no useful

work done by the CPU from the user's perspective. Therefore, context switching is sheer overhead in this condition.

## a) Theory

## b) Practice

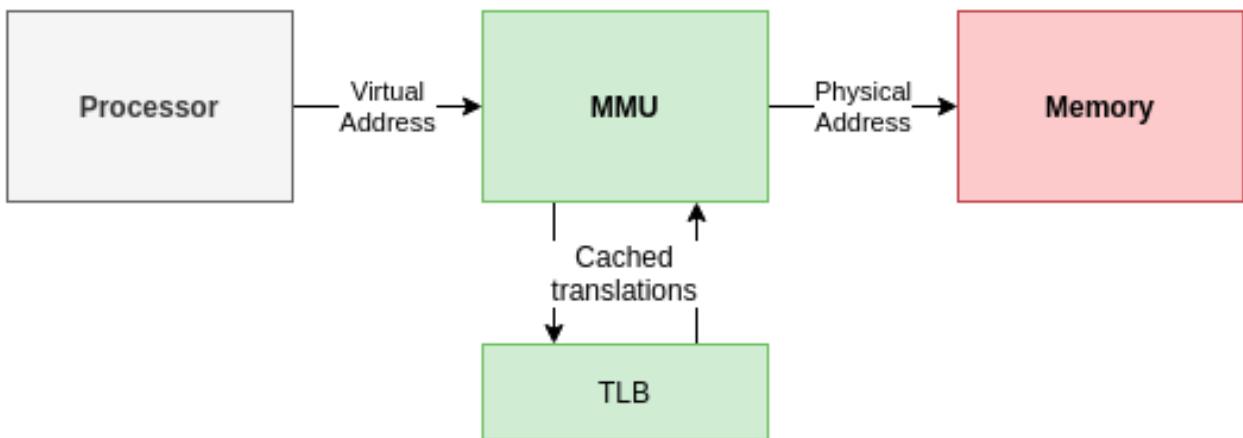

### 8.4.1. Translation Lookaside Buffer

Translating a virtual address to a physical address is expensive. The processor must access the pages table structures, which usually have 3-4 levels. Thus, a single memory access actually requires 4-5 memory accesses.

To mitigate this issue, most modern processors cache virtual-to-physical translations in a translation lookaside buffer (TLB). The TLB is part of the MMU and can be understood as a cache for the MMU.

When virtual memory is updated - for instance, when one process's address space is replaced with another's during a software context switch - the TLB suddenly contains "stale" translations that are no longer valid. These translations must be flushed for correct behavior. This is less than ideal, as the next few operations must wait for the slow virtual-to-physical translations.

Recent Intel and AMD processors sport a tagged TLB, which allows you to tag a given translation with a certain address space configuration. In this scheme TLB entries never get "stale", and thus there is no need to flush the TLB.

#### 8.4.2. Address Space Identifier

On ARM systems, this TLB tagging mechanism is implemented as follows: a value called address space identifier (ASID) is assigned by the OS to each task, so the MMU can distinguish between memory pages which share the same virtual address. For ARMv7 systems in particular, the ASID is an eight-bit value. For ARMv8, it can be 8 or 16 bits in length. The presence of the ASID in the TLB allows it to identify for each entry which Address Space it belongs to. When it comes to context switching, one of the necessary steps in the switching of task context is making sure the translation process using TLB, won't translate to a physical address of another address space. One of the solutions is to use and update the current ASID value, identifying if an entry in cache should or not be used. In some system implementations, ASID values might be ignored altogether, in this case, the solution to this problem is to just invalidate the whole TLB cache, always resulting in page-faults and fetching the translation data from the correct process page table.

When using the short-descriptor translation table, the ASID value is stored in the CONTEXTIDR register. In case of the long-descriptor, TTBR0 register is a 64 bits register and it also stores the current ASID value.

##### 8.4.2.1. ASID on Context Switch

Below we present two implementations for updating the process page table address and the ASID value.

|||||||

Change Translation Table Base Register to the global-only mappings ISB Change ASID to new value ISB Change Translation Table Base Register to new value

In the first example, the address of the translation table (page table) is changed to a translation table that only global-pages could be accessed or translated, ensuring that no non-global pages can be fetched, because and it is uncertain if the old or new address space would be used for translating virtual addresses.

|||||||

Change ASID to 0 ISB Change Translation Table Base Register ISB Change ASID to new value

In the second example, the ASID value is set to zero, which is a value normally not used for any operations and there should not exist any entries on TLB with such ASID. In this situation, we also ensure that translation would occur correctly, since translation will have to access the translation table.

##### 8.4.2.2. Limitation of ASID

In some cases, the ASID value is represented by 8 bit, therefore, there can only be 256 different address spaces, since we only have 256 different identifiers. Because, most likely, processes do not share address spaces with each other, as a result, we are also bound to have up to 256 different tasks running at once in the system. The long-descriptor is a solution to this problem, because it offers not 8 but 16 bits for address space identifiers.

Linux uses a rollover mechanism for ASID, where once the ASID options run out, ASID values are invalidated from the branch predictor, caches and TLBs, and should be allocated again for each process, offering a chance for processes without an ASID (unable to run) to get one.

## 8.5. Switching Context in ARMv7/Raspberry Pi3

### 8.5.1. ARM Processor Mode

The ARM processor has many execution modes, this is important for task context switching because some of the indispensable register read and write requires it to be running on a privileged mode. Also, privileged modes offer banked registers that allow easier stack manipulation. A process running on user mode will have to enter a privileged mode by an interrupt before switching context. IRQ timer interrupt will bring the processor to IRQ mode, this is an example of an interrupt that can be used to achieve a privileged reschedule. Also, system mode has no banked register, this mode allows to update stack pointer registers, among others, for the next user process while in a privileged mode.

### 8.5.2. IRQ

IRQ handlers or interrupt request handlers is a hardware signal sent to the processor that temporarily stops a running program and allows a special program, an interrupt handler, to run instead hardware interrupts are used to handle events such as receiving data from a modem or network card, key presses, or mouse movements.

In the general case to enter a exception handler, we first must: